# **Sundance Multiprocessor Technology Limited Product Specification**

| Unit / Module Description:    | Dual ADC (14bits/250MSPS) and Dual DAC (16bits/800MSPS) SLB Module |  |

|-------------------------------|--------------------------------------------------------------------|--|

| Unit / Module Number:         | SMT943                                                             |  |

| <b>Document Issue Number:</b> | 2                                                                  |  |

| Issue Date:                   | 20/04/2009                                                         |  |

| Original Author:              | P S Robert                                                         |  |

# Product Specification for SMT943

Sundance Multiprocessor Technology Ltd, Chiltern House, Waterside, Chesham, Bucks. HP5 1PS.

This document is the property of Sundance and may not be copied nor communicated to a third party without prior written permission.

© Sundance Multiprocessor Technology Limited 2008

Form: QCF51

Date: 6 January 2008

# **Revision History**

| Issue | Changes Made             | Date     | Initial<br>s |

|-------|--------------------------|----------|--------------|

| 1     | Initial Document created | 26/05/08 | PhSR         |

| 2     | Part numbers corrected   | 20/04/09 | PhSR         |

|       |                          |          |              |

# **Table of Contents**

| 1  |          | Introduction                            | <b>.</b> 5 |

|----|----------|-----------------------------------------|------------|

| 2  |          | Related Documents                       | . 5        |

|    | 2.1      | Referenced Documents                    | 5          |

|    | 2.2      | Applicable Documents                    | 6          |

| 3  |          | Acronyms, Abbreviations and Definitions | 6          |

|    | 3.1      | Acronyms and Abbreviations              | 6          |

|    | 3.2      | Definitions                             | 6          |

| 4  |          | Functional Description.                 | 6          |

|    | 4.1      | Block Diagram                           | 6          |

|    | 4.2      | Module Description                      | 6          |

|    | 4.3      | Interface Description                   | 7          |

|    | 4        | 4.3.1 Mechanical Interface              | 7          |

|    | 4        | 4.3.2 Electrical Interface              | 7          |

| 5  |          | Verification Procedures                 | . <b>7</b> |

| 6  |          | Review Procedures                       | , <b>7</b> |

| 7  |          | Validation Procedures                   | , <b>7</b> |

| 8  |          | Timing Diagrams                         | , <b>7</b> |

| 9  |          | Circuit Description / Diagrams          | , <b>7</b> |

| 10 | )        | Footprint                               | 8          |

|    | 10.      | 1 Top View                              | 8          |

|    | 10.      | 2 Bottom View                           | 9          |

| 11 |          | Pinout                                  | 10         |

| 12 | ;        | Support Packages                        | 10         |

| 13 | }        | Physical Properties                     | lO         |

| 14 | ļ        | Safety 1                                | 10         |

| 15 | <b>.</b> | EMC                                     | 10         |

# **Table of Figures**

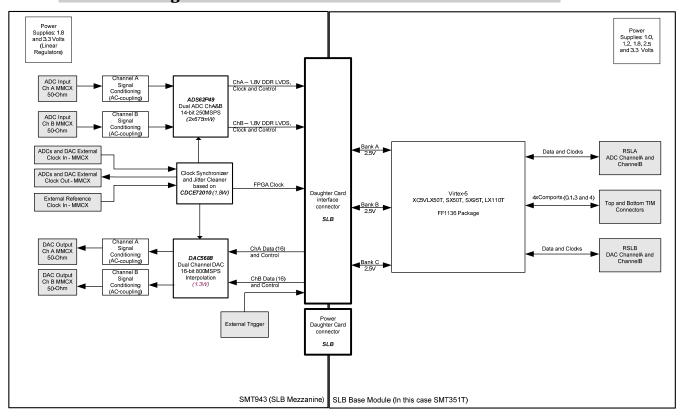

| Figure 1 - Block diagram.         | 6 |

|-----------------------------------|---|

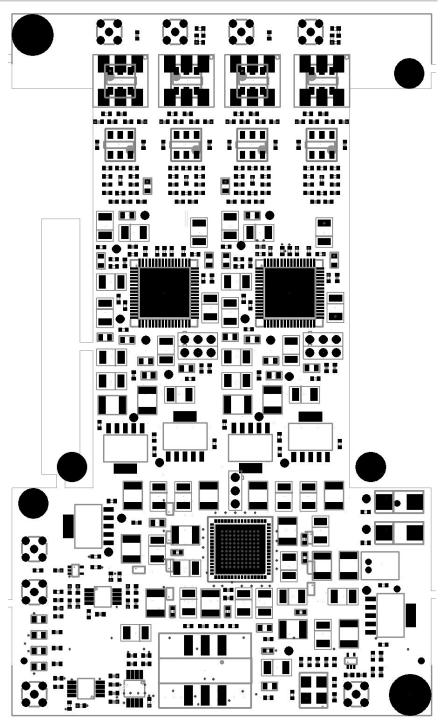

| Figure 2 - Layout - Top Layer.    | Q |

|                                   |   |

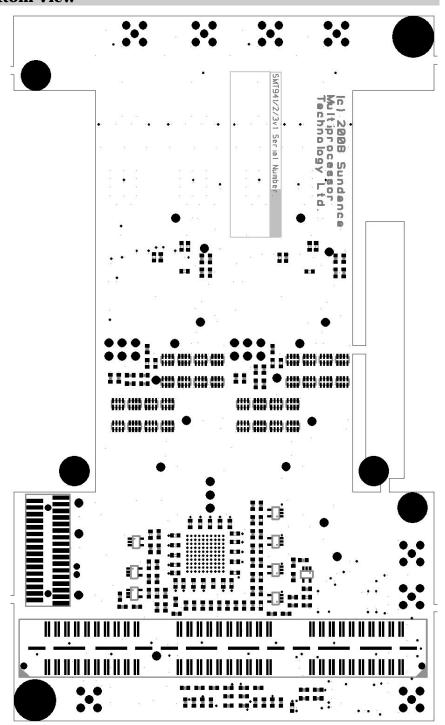

| Figure 3 - Layout - Bottom Layer. | 9 |

### 1 Introduction

The *SMT943* is a single width expansion TIM that plugs onto an <u>SLB</u> base module, the <u>SMT351T</u> (Virtex-5 LXT or SXT FPGA) as an example and incorporates 2 Analog-to-Digital Converters (<u>ADS62P49</u>) and a Texas Instrument dual-channel Digital-to-Analog Converter (<u>DAC5688</u>). The *SMT943* implements a comprehensive clock circuitry based on a chip (<u>CDCE72010</u>) from Texas instrument that allows synchronisation among the converters and the use of an external reference clock. It provides a complete conversion solution and stands as a platform that can be part of a transmit/receive base station. The SMT943 has an on-board VCXO of frequency 245.76MHz.

ADCs are 14-bit and can sample at up to 250 MHz. The DAC has a resolution of 16 bits and is able to update outputs at up to 800MHz. All converters are 1.8/3.3-Volt.

The <u>Xilinx FPGA</u> (Virtex-5 LXT or SXT series in the case of the SMT351T) on the base module is responsible for handling data going/coming to/from one of the following destination/source: converters, Comports, **Rocket Serial Link** (<u>RSL</u>). These interfaces are compatible with a wide range of Sundance's modules.

The memory (DDR2) on the base module can store incoming and/or outgoing samples.

Converter configuration, sampling and transferring modes are set via internal control registers stored inside the FPGA and accessible via Comport.

The SMT943 module is well-suited for multi-carrier, wide bandwidth communication applications.

### 2 Related Documents

### 2.1 Referenced Documents

ADC datasheet. <u>Texas Instrument ADS62P49</u>. DAC datasheet: <u>Texas Instrument DAC5686</u>. Clock datasheet: <u>Texas Instrument CDCE72010</u>.

### 2.2 Applicable Documents

# 3 Acronyms, Abbreviations and Definitions

- 3.1 Acronyms and Abbreviations

- 3.2 Definitions

# 4 Functional Description

### 4.1 Block Diagram

Figure 1 - Block diagram.

### 4.2 Module Description

The dual channel ADC (ADS62P49) has a resolution of 14 bits and can sample at up to 250 MHz. The chip incorporates a programmable fine gain of up to 6dBs for SNR/SFDR trade-off, a DC offset correction and an internal voltage reference. The ADC has got internal registers to implement the above functionalities and are accessible via a serial interface controlled by the FPGA on the SLB base module.

The dual channel DAC (<u>DAC5688</u> – Texas Instrument) has integrated 2x-8x interpolation filters, a fine frequency mixer with a 32-bit complex numerically controlled oscillator, an on-board clock multiplier, an IQ compensation and an internal voltage reference.

- 4.3 Interface Description

- 4.3.1 Mechanical Interface

- 4.3.2 Electrical Interface

- 5 Verification Procedures

- **6 Review Procedures**

- 7 Validation Procedures

- 8 Timing Diagrams

- 9 Circuit Description / Diagrams

# **10 Footprint**

### 10.1 Top View

Figure 2 - Layout - Top Layer.

### 10.2 Bottom View

Figure 3 - Layout - Bottom Layer.

### 11 Pinout

# 12 Support Packages

# 13 Physical Properties

| Dimensions      |       |  |

|-----------------|-------|--|

| Weight          |       |  |

| Supply Voltages |       |  |

| Supply Current  | +12V  |  |

|                 | +5V   |  |

|                 | +3.3V |  |

|                 | -5V   |  |

|                 | -12V  |  |

| MTBF            |       |  |

# 14 Safety

This module presents no hazard to the user when in normal use.

### **15 EMC**

This module is designed to operate from within an enclosed host system, which is build to provide EMC shielding. Operation within the EU EMC guidelines is not guaranteed unless it is installed within an adequate host system.

This module is protected from damage by fast voltage transients originating from outside the host system which may be introduced through the output cables.

Short circuiting any output to ground does not cause the host PC system to lock up or reboot.