# Sundance Multiprocessor Technology Limited **Product Specification**

| Unit / Module Description: TIM & SLB Carrier |                                |  |

|----------------------------------------------|--------------------------------|--|

| Unit / Module Number:                        | SMT111                         |  |

| Document Issue Number:                       | 1.2.6                          |  |

| Issue Date:                                  | 4 <sup>th</sup> September 2009 |  |

| Original Author:                             | G Parker                       |  |

# Product Specification for SMT111

Sundance Multiprocessor Technology Ltd, Chiltern House, Waterside, Chesham, Bucks. HP5 1PS.

This document is the property of Sundance and may not be copied nor communicated to a third party without prior written permission.

© Sundance Multiprocessor Technology Limited 2006

Last Edited: 04/09/2009 16:43:00

Form: OCF51

Date: 6 July 2006

# **Revision History**

| Issue | Changes Made                                       | Date     | Initials |

|-------|----------------------------------------------------|----------|----------|

| 1.0   | First release.                                     | 10/09/07 | GKP      |

| 1.1   | Added UART and 4 RS232 transceivers.               | 23/10/07 | GKP      |

|       | Added 4 user LEDs to board.                        |          |          |

| 1.2   | Replaced CPLD with Spartan-3.                      | 9/11/07  | GKP      |

|       | Added DIP switch to FPGA.                          |          |          |

|       | Made the JTAG Out connector dual function.         |          |          |

|       | Added a microSD socket.                            |          |          |

| 1.2.1 | Moved ComPort from SLB connector.                  | 9/11/07  | GKP      |

|       | Corrected title page header.                       |          |          |

|       | Split the UART and USB buses in the block diagram. |          |          |

| 1.2.2 | RSL section added.                                 | 31/1/08  | GKP      |

|       | Related documents expanded.                        |          |          |

| 1.2.3 | Added reference to suitable power supply.          | 6/2/08   | GKP      |

| 1.2.4 | Updated RS232 connector pin-out.                   | 13/2/08  | GKP      |

|       | Removed reference to an external reset signal.     |          |          |

|       | Added a DIP switch table.                          |          |          |

| 1.2.5 | Added power connector drawing and part number.     | 10/4/08  | GKP      |

| 1.2.6 | Modified: Comport connected to SLB connector       | 04/09/09 | SM       |

| Important comments or cautions are displayed next to this symbol. |

|-------------------------------------------------------------------|

# **Table of Contents**

| 1  | Introduction / Description                   | 4  |

|----|----------------------------------------------|----|

| 2  | Related Documents                            | 4  |

| 3  | Acronyms, Abbreviations and Definitions      | 4  |

| 4  | Functional Description                       | 5  |

|    | 4.1 Block Diagram                            | 5  |

|    | 4.2 Module Description                       | 6  |

|    | 4.2.1 Xilinx FPGA                            | 6  |

|    | 4.2.2 USB2                                   | 6  |

|    | 4.2.3 Quad UART                              | 6  |

|    | 4.2.4 Flash                                  | 7  |

|    | 4.2.5 JTAG In/Out (TTL I/O)                  | 7  |

|    | 4.2.6 TIM                                    | 7  |

|    | 4.2.7 SLB                                    | 7  |

|    | 4.2.8 RSL                                    | 8  |

|    | 4.2.9 Power                                  | 8  |

|    | 4.2.10LEDs                                   | 9  |

|    | 4.2.11Reset                                  | 9  |

|    | 4.2.12DIP Switch                             | 9  |

| 5  | Verification, Review & Validation Procedures | 10 |

| 6  | Circuit Description / Diagrams               | 10 |

| 7  | Footprint                                    | 11 |

|    | 7.1 Top View                                 | 11 |

|    | 7.2 Bottom View                              | 11 |

| 8  | Support Packages                             | 12 |

| 9  | Physical Properties                          | 12 |

| 1( | ) Safety                                     | 13 |

| 11 | EMC                                          | 13 |

| 12 | 2 Ordering Information                       | 13 |

# 1 Introduction / Description

The SMT111 is a carrier board capable of accepting a single TIM and SLB mezzanine module.

A single 12Vdc power input is required, and on-board converters produce the necessary TIM supplies.

The main features of the SMT111 are listed below:

☐ TIM & SLB Carrier.

☐ Single 12Vdc power requirement.

☐ TIM ComPorts connect to SLB.

☐ USB2 Interface to TIM ComPort.

☐ UART and RS232 interfaces.

□ JTAG In/Out.

☐ Flash to store TIM configuration/application.

### 2 Related Documents

Sundance Local Bus (SLB) specification:

**SLB** Specification.

Texas Instruments Module specification.

SMT118: Carrier with 3 Module sites and I/O facilities.

**SMT144**: Carrier with 4 Module sites.

SMT148FX: Carrier with 4 Module sites.

SMT6048: USB Driver

# 3 Acronyms, Abbreviations and Definitions

A list of acronyms etc:

http://www.sundance.com/web/files/static.asp?pagename=acc

# 4 Functional Description

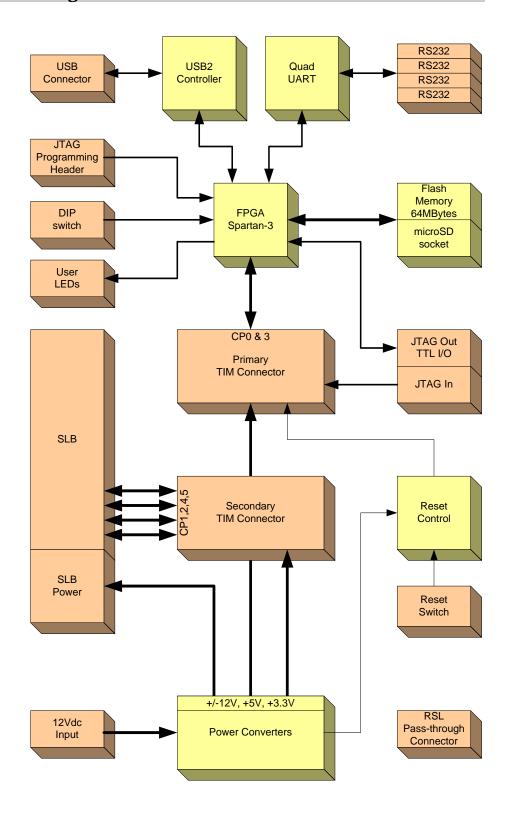

The major elements of the SMT111 are shown in the block diagram below.

# 4.1 Block Diagram

### 4.2 Module Description

### 4.2.1 Xilinx FPGA

A Xilinx Spartan-3 XC3S200 FPGA provides the interface between a TIM ComPort and the USB and UART controllers.

The FPGA design for the USB interface is used on the SMT148FX carrier board, and allows applications (Diamond) to be downloaded to the TIM.

For UART configurations, a simple protocol will be used to access the internal registers.

The FPGA operating mode (flash programming, USB, UART) in controlled via a 4-way switch.

### 4.2.2 USB2

A Cypress CY7C68013A is used to implement a USB2 interface. This device operates with a Xilinx FPGA to provide a communication path to the TIM via ComPort3.

This interface can operate at up to 48MB/s.

Programs can be loaded and executed via this port using 3L's Diamond server

### 4.2.3 Quad UART

An Oxford Semiconductor 16C954 UART provides 4 RS232 channels.

Maxim MAX3241 devices perform the conversion from 3.3V LVTTL to true RS232 signal levels.

The RS232 signals are available via latching IDC headers. The pin-out is shown here:

| Signal | Pin | Pin | Signal |

|--------|-----|-----|--------|

|        |     |     |        |

| DCD    | 1   | 2   | RX     |

| TX     | 3   | 4   | DTR    |

| GND    | 5   | 6   | DSR    |

| RTS    | 7   | 8   | CTS    |

| RI     | 9   | 10  | -      |

| The 10 pin IDC headers do NOT have the standard pin-out required for a direct connection to a 9 way d-connector |

|-----------------------------------------------------------------------------------------------------------------|

|                                                                                                                 |

### 4.2.4 Flash

The Xilinx FPGA is coupled to a 64Mbyte flash to enable configuration of FPGA only TIMs, or to store DSP applications and additional FPGA configurations.

A separate microSD (transflash) socket connects directly to the FPGA. No FPGA IP is provided as standard, but with the addition of a MicroBlaze processor, a full FAT file system could be implemented.

### 4.2.5 JTAG In/Out (TTL I/O)

An XDS510/560 compatible 14-way 0.1" pitch DIL pin header is provided to enable debugging of a DSP TIM using Code Composer Studio.

A JTAG Out connector can be used to chain this carrier with any other Sundance carrier board. JTAG chaining is handled by the Xilinx FPGA.

The JTAG Out connector can be used to carry general purpose LVTTL I/O signals. The selection of JTAG\_Out or LVTTL\_I/O is made by the DIP switch.

### 4.2.6 TIM

A single TIM site can accept any of Sundance's FPGA or DSP modules.

ComPort 3 is routed to the USB2 interface. The remaining ComPorts are connected to the SLB connector.

### 4.2.7 SLB

Forty eight signals from the SLB are connected to 4 ComPorts on the TIM connector (ComPorts 1, 2, 4 & 5).

These are all LVTTL compatible.

As all DSP and FPGA modules that Sundance produce use FPGAs to communicate via ComPorts, the SLB signals are therefore available directly by this FPGA.

### 4.2.8 RSL

A pair of RSL connectors are provided on the top and bottom of the carrier. Four lanes of RSL signals are simply connected from the top (TIM side) to the bottom. This allows access to the TIM's underside RSL signals.

### **4.2.9 Power**

A single 12Vdc power source is needed. E.g. the MW174series from SL Power Electronics. http://www.slpower.com/ProductView.aspx?ProductID=295

On-board converters provide the following voltages:

| +12V  | 1.0A  |

|-------|-------|

| -12V  | 0.75A |

| +5V   | 16A   |

| +3.3V | 16A   |

This is sufficient power to provide up to 80W of power for FPGA TIMs (if Vcore is derived from +5V).

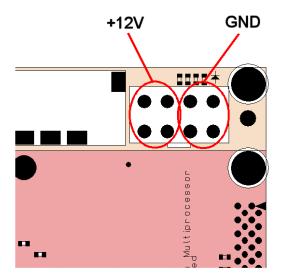

The power input connector (Molex 39-28-1083, MINI-FIT, 8-way) pin-out is shown here:

### 4.2.10 LEDs

4 user LEDs are connected directly to the FPGA.

### 4.2.11 Reset

Reset is asserted during power up, or by pressing the reset switch.

### **4.2.12 DIP Switch**

A four position DIP switch allows for the following settings:

| SW | Setting   |          |  |

|----|-----------|----------|--|

|    | ON        | OFF      |  |

| 1  | LVTTL I/O | JTAG-OUT |  |

| 2  |           |          |  |

| 3  |           |          |  |

| 4  |           |          |  |

# 5 Verification, Review & Validation Procedures

To be carried out in accordance with the Sundance Quality Procedures (ISO9001).

# 6 Circuit Description / Diagrams

# 7 Footprint

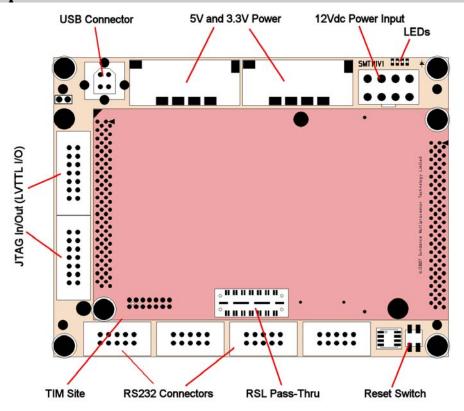

### 7.1 Top View

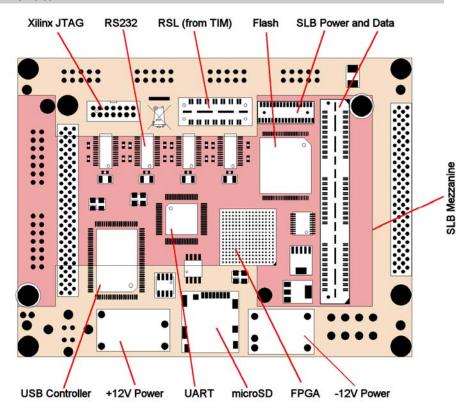

### 7.2 Bottom View

# 8 Support Packages

# 9 Physical Properties

+3.3V

-5V

-12V

| Dimensions | 118.6mm | 90.0mm |

|------------|---------|--------|

|            |         |        |

| Weight     |         |        |

|            | •       |        |

| Voltage    | Current |        |

|            |         |        |

| +12V       | TBD     |        |

| +5V        | TBD     |        |

| MTBF |  |

|------|--|

TBD

TBD

TBD

# 10 Safety

This module presents no hazard to the user when in normal use.

### **11 EMC**

This module is designed to operate from within an enclosed host system, which is build to provide EMC shielding. Operation within the EU EMC guidelines is not guaranteed unless it is installed within an adequate host system.

This module is protected from damage by fast voltage transients originating from outside the host system which may be introduced through the output cables.

Short circuiting any output to ground does not cause the host PC system to lock up or reboot.

# **12 Ordering Information**

Order number:

SMT111