# Sundance Multiprocessor Technology Limited **Design Specification**

Form: QCF51

Dated: 20 December 2001

Revision: 5.1

Approved: Mark Ainsworth

| Unit / Module Name:   | 8 TIM site stand-alone carrier |  |

|-----------------------|--------------------------------|--|

| Unit / Module Number: | SMT180                         |  |

| Used On:              | SMT8180                        |  |

| Document Issue:       | 2.00                           |  |

| Date:                 | 7 <sup>th</sup> February 2005  |  |

# **CONFIDENTIAL**

| Approvals         |  | Date |

|-------------------|--|------|

| Managing Director |  |      |

| Software Manager  |  |      |

| Design Engineer   |  |      |

Sundance Multiprocessor Technology Ltd, Chiltern House, Waterside, Chesham, Bucks. HP5 1PS. This documents is the property of Sundance and may not be copied nor communicated to a third party without the written permission of Sundance. © Sundance Multiprocessor Technology Limited 1999

# **Revision History**

|          | Changes Made                                | Issue | Initials |

|----------|---------------------------------------------|-------|----------|

| 1-7-03   | First version.                              | 1.00  | GP       |

| 1-7-03   | Added comm port diagram.                    | 1.01  | GP       |

| 3-7-03   | Updated comm port drawing.                  |       | GP       |

|          | Added comm port connector pin-out.          |       |          |

|          | Updated PCB layout drawing.                 |       |          |

| 17-7-03  | Added IIOF connectivity                     | 1.03  | GP       |

| 12-5-04  | Updated PCB layout.                         |       | GP       |

|          | Amended power supply connector pin-out.     |       |          |

| 12-5-04  | Added power connector picture and hyperlink | 1.05  | GP       |

| 21-10-04 | Power consumption section added.            | 1.06  | GP       |

| 2-11-04  | Power connector part numbers added.         | 1.07  | GP       |

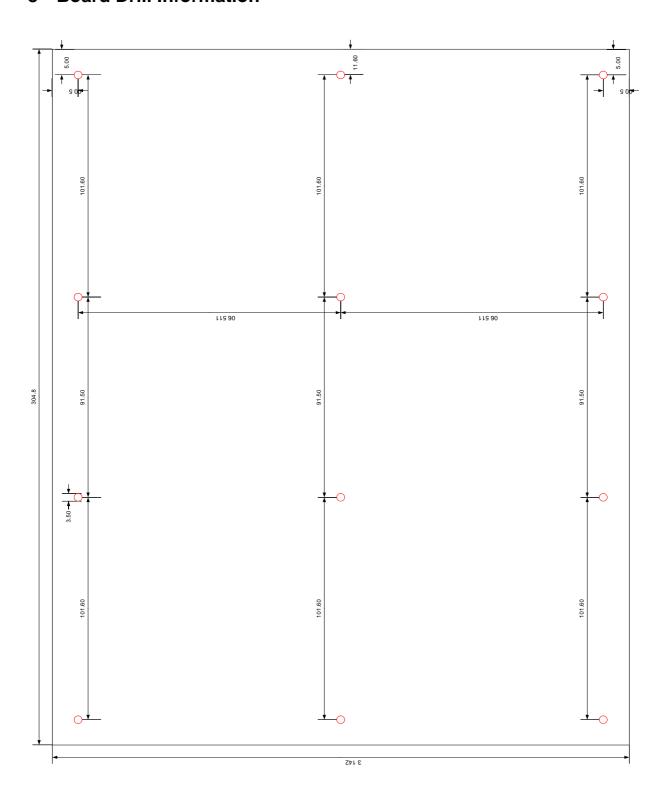

| 7-02-05  | Added PCB drill information                 | 2.00  | GP       |

# **Table of Contents**

| 1  | In                        | ntroduction           | 4  |  |  |

|----|---------------------------|-----------------------|----|--|--|

|    | 1.1                       | Overview              | 4  |  |  |

|    | 1.2                       | Related Documents     | 4  |  |  |

| 2  | Fι                        | unctional Description | 5  |  |  |

|    | 2.1                       | Comm Port Diagram     | 5  |  |  |

|    | 2.2                       | Power supplies        | 6  |  |  |

|    | 2.3                       | JTAG                  | 6  |  |  |

|    | 2.4                       | Flash Memory          | 6  |  |  |

|    | 2.5                       | Fan Power             | 7  |  |  |

|    | 2.6                       | External Comm-Ports   | 7  |  |  |

|    | 2.7                       | Reset Scheme          | 7  |  |  |

|    | 2.8                       | IIOF Connectivity     | 8  |  |  |

| 3  | Po                        | ower Consumption      | 9  |  |  |

| 4  | Verification Procedures9  |                       |    |  |  |

| 5  | Review Procedures9        |                       |    |  |  |

| 6  | S Validation Procedures   |                       |    |  |  |

| 7  | PCB Layout Details10      |                       |    |  |  |

| 8  | Board Drill Information11 |                       |    |  |  |

| 9  | Safety12                  |                       |    |  |  |

| 1( | 0                         | EMC                   | 12 |  |  |

# 1 Introduction

#### 1.1 Overview

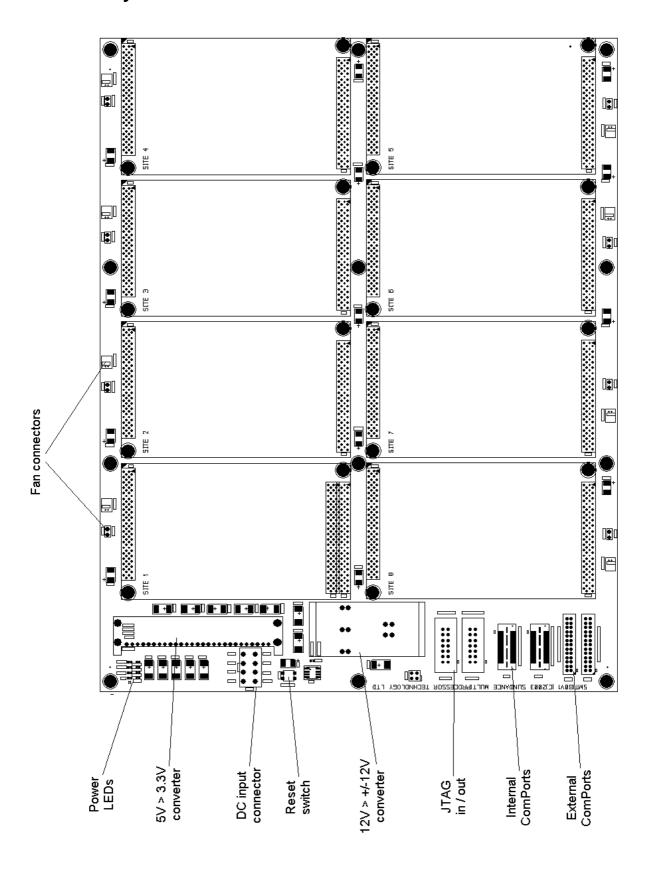

The SMT180 is an 8 site TIM carrier board.

Connectors are provided to interface to;

- 10/100 Ethernet

- JTAG.

#### 1.2 Related Documents

Texas Instruments Module specification.

# 2 Functional Description

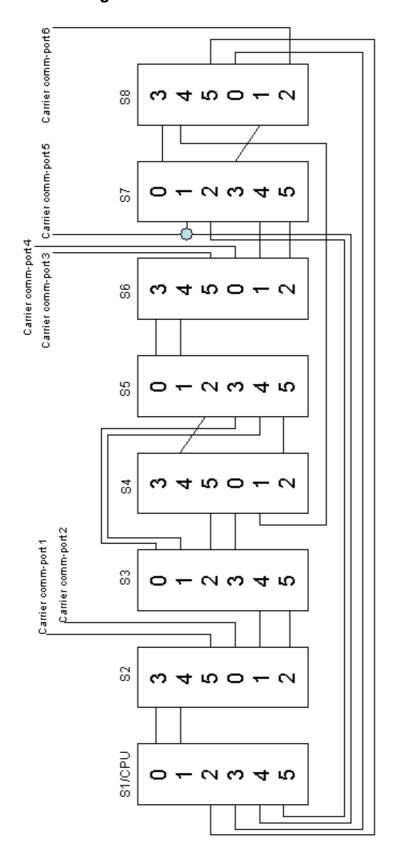

### 2.1 Comm Port Diagram

#### 2.2 Power supplies

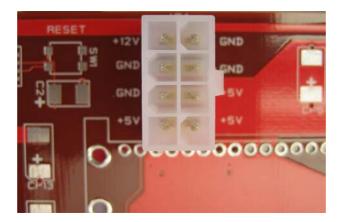

Power is supplied from external +5 and +12V sources. This enters the board via an 8-pin Molex Mini-Fit Jr. dual-in-line pin header (Molex mini fit 8 way, 39-28-1083).

The mating part to this connector is a Molex 39-01-2080 (Farnell order code 151-869 + 8 off 39-00-0039, Farnell 151-890).

| Signal | Pin<br>number | Pin<br>number | Signal |

|--------|---------------|---------------|--------|

| 12V    | 7             | 8             | GND    |

| GND    | 5             | 6             | GND    |

| GND    | 3             | 4             | 5V     |

| 5V     | 1             | 2             | 5V     |

The +12V source is input to a DC-DC converter module, which produces +/-12V to the TIM sites.

The +5V source is used to supply the TIM sites directly, and also as input to two DC-DC converters that produce the 3.3V supply to the TIM sites.

Each pin is capable of carrying 7A.

#### **2.3 JTAG**

A single JTAG chain connects all 8 TIM sites and also to JTAG in & out connectors. This chain is used with the TI Code Composer Studio software suite.

The JTAG-out connector can be connected to the JTAG-in connector of other SMT180s, thus extending the chain.

#### 2.4 Flash Memory

A 64Mbit flash memory is provided which interfaces to the primary/root TIM site's global connector.

#### 2.5 Fan Power

Eight two-pin connectors are provided to supply fans with a +12V supply.

#### 2.6 External Comm-Ports

Two 24-pin dual-in-line 2mm pitch (latching) connectors are provided which are shown in the comm port diagram as *carrier comm-port 5 and 6*. These connectors have the following pin-out.

|           | Pin number | Pin number |     |

|-----------|------------|------------|-----|

| CSTRB     | 1          | 2          | GND |

| CRDY      | 3          | 4          | GND |

| CREQ      | 5          | 6          | GND |

| CACK      | 7          | 8          | GND |

| D0        | 9          | 10         | D1  |

| D2        | 11         | 12         | D3  |

| D4        | 13         | 14         | D5  |

| D6        | 15         | 16         | D7  |

| 3.3V      | 17         | 18         | GND |

| /RESETOUT | 19         | 20         | GND |

| /RESETIN  | 21         | 22         | GND |

| NC        | 23         | 24         | NC  |

#### 2.7 Reset Scheme

A power rail monitor observes the state of the 3.3V supply. This device will generate a reset to the SMT180 (RESET180) during power-up or if the 3.3V supply drops below 3V. This signal is an open-collector output and is also driven to the inter-card comm-port connectors, and thus to another SMT180.

The POR (power on reset) signal is driven to the RESETOUT pin on the external comm port connector.

The RESETIN pin on the above connector is buffered by an open-collector device which in turn can also drive the RESET180 signal.

An additional 4 pin header is provided to allow other devices to share the open-collector RESET180 signal.

See the circuit diagrams for full details.

### 2.8 IIOF Connectivity

Each TIM site provides 3 interrupt pins, IIOF0, 1 & 2.

IIOF0 & 1 are connected in a daisy-chain with TIM site 1 IIOF0 connected to TIM site 2 IIOF1; TIM site 2 IIOF0 connected to TIM site 3 IIOF1; etc; finishing with TIM site 8 IIOF0 connected to TIM site 1 IIOF1.

All TIM site's IIOF2 signals are connected together.

#### 3 Power Consumption

The SMT180 requires two power supplies, 5V & 12V.

The 5V supply is used to provide the TIM sites directly with 5V. A Texas Instruments PT7711 device is used to convert the 5V to 3.3V, which is then used for the TIM sites and on-board logic. This device has a dc-dc conversion efficiency of 93%.

Without any TIMs fitted, the 5V supply will consume 74mA.

The 12V supply is used to provide power directly to the fan connectors (fans not supplied) and, via an Astec AEE00BB12-4 device, +/-12V to the TIM sites. This device has a dc-dc conversion efficiency of 84%.

Without any TIMs fitted, the 12V supply will consume 20mA.

This gives a total power consumption of about 0.6W.

Note that when TIMs are added, the power consumption will increase by the power requirements of the TIMs divided by the efficiency of the SMT180's power supplies.

Example: If you add a TIM that requires 1A@ 12V and 2A@ 3.3V, then the additional power consumption would be;

1\*12/0.84 + 2\*3.3/0.93 = 21.4W.

#### 4 Verification Procedures

The specification (design requirements) will be tested using the following:

1) Running Code Composer Studio

#### 5 Review Procedures

Reviews will be carried out as indicated in design quality document QCF14 and in accordance with Sundance's ISO9000 procedures.

#### 6 Validation Procedures

# 7 PCB Layout Details

# **8 Board Drill Information**

### 9 Safety

This module presents no hazard to the user.

#### **10 EMC**

This module is designed to operate from within an enclosed host system, which is build to provide EMC shielding. Operation within the EU EMC guidelines is not guaranteed unless it is installed within an adequate host system.

This module is protected from damage by fast voltage transients originating from outside the host system which may be introduced through the output cables.

Short circuiting any output to ground does not cause the host PC system to lock up or reboot.