# Sundance Multiprocessor Technology Limited Application note

SUNDANCE

| Unit / Module Description: | SMT 339          |

|----------------------------|------------------|

| Document Issue Number:     | 1                |

| Issue Date:                | 25/09/07         |

| Original Author:           | Francois Godreau |

### CODESIGN, IMPLEMENTATION AND VALIDATION OF THE XILINX FPGA'S EMBEDDED DEVICES FOR SIGNAL PROCESSING SOLUTIONS

Sundance Multiprocessor Technology Ltd, Chiltern House, Waterside, Chesham, Bucks. HP5 1PS.

This document is the property of Sundance and may not be copied nor communicated to a third party without prior written permission. © Sundance Multiprocessor Technology Limited 2006

Certificate Number FM 55022

# Abstract

The design team develops rapid prototyping platforms for high-performance processing. These boards are independent modules populated by DSPs and FPGAs that can be interconnected via communication links. Sundance boards are typically based on TI DSP and Xilinx FPGAs which embed processors like the PowerPC or Microblaze.

Sundance provides basic software support for their modules. To complement this software, Sundance works in partnership with software companies. These companies provide highlevel design tools and methodologies that accelerate the design of applications based on a mixed DSP and FPGA systems. Although these companies provide solutions for the DSPs and FPGAs in the Sundance systems, no support for the PowerPC has yet been developed.

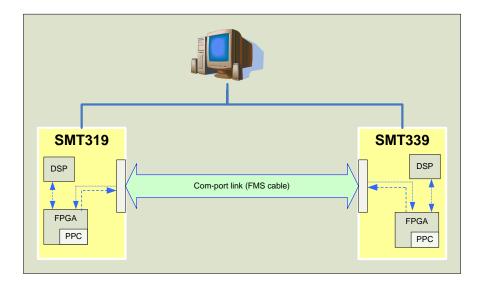

The Sundance SMT339 provides a TI DSP DM642 and a Xilinx FPGA-FX60 with two embedded PowerPCs which formed an ideal development platform for this application note. In addition to the SMT339, a SMT319 module was used to communicate with this design in the PowerPC. The SMT319 was connected to a host system on which debug information could be printed out. XILINX tools were used such as EDK to implement the embedded processor and XILINX ISE software to design the application.

Sundance FPGAs implements several types of communication resources that are used to communicate between modules. These are comport, SHB, SDB, RSL and SLB.

Keywords: FPGA; PowerPC, Microblaze, firmware, co-design, embedded processors

# **Table of contents**

| INTRODUCTION                         | <u>8</u> |

|--------------------------------------|----------|

| TABLE                                | 7        |

| 1 PROJECT DESCRIPTION                | <u></u>  |

| 1.1 THE MAIN OBJECTIVE               | 9        |

| 1.2 REQUIREMENT                      |          |

| 1.2.1 Processor choice               |          |

| 1.2.2 Communication resources        |          |

| 1.2.3 External memory                |          |

| 1.3 BACKGROUND                       |          |

| 1.3.1 Embedded processor             |          |

| 1.3.2 External ZBT memory            |          |

| 1.4 TEST BENCH CONFIGURATION         |          |

| 1.4.1 HARDWARE SET UP                |          |

| 1.4.2 Software set up                |          |

| 1.5 DESIGN IMPLEMENTATION            |          |

| 1.5.1 PowerPC block                  |          |

| 1.5.2 Comport link implementation    |          |

| 1.5.3 External ZBT memory controller |          |

| 1.5.4 Global implementation          |          |

| CONCLUSION                           | <u></u>  |

| REFERENCES                           |          |

# **Table of figures**

| Figure 1 design expected                                          | . 14 |

|-------------------------------------------------------------------|------|

| Figure 2 PowerPC hard processor                                   | . 15 |

| Figure 3 PowerPC405Fx block diagram                               | . 16 |

| Figure 4 CoreConnect bus architecture                             | . 17 |

| Figure 5 PowerPC405 CPU and CoreConnect based SOC example         |      |

| Figure 6 ZBT memory block diagram                                 |      |

| Figure 7 timing feature of the ZBT memory                         |      |

| Figure 9 SMT339 diagram block                                     |      |

| Figure 10 Simplified ISE / EDK Design Flow                        | . 24 |

| Figure 11 development cycle with Code Composer Studio             | . 25 |

| Figure 12 system assembly view                                    |      |

| Figure 13 blocks connexions                                       | . 28 |

| Figure 14 Block diagram PowerPC - GPIO                            | . 29 |

| Figure 15 application tab                                         |      |

| Figure 16 XPS output widows - software compiled                   | . 30 |

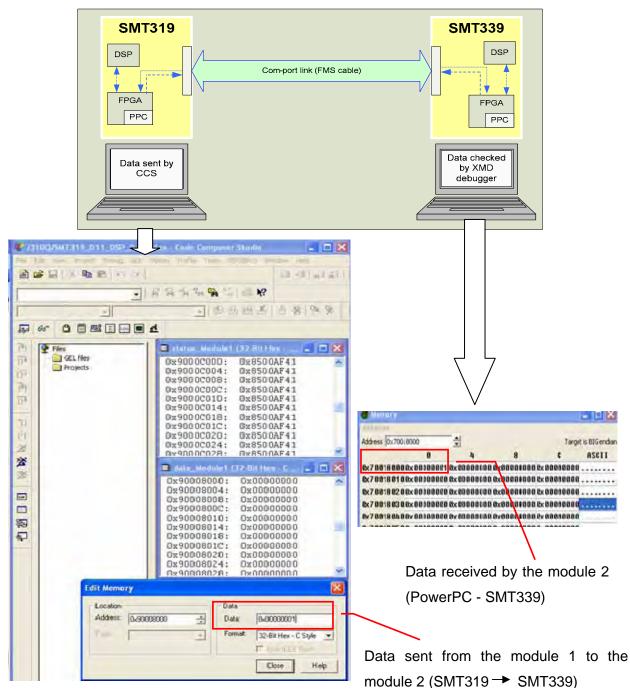

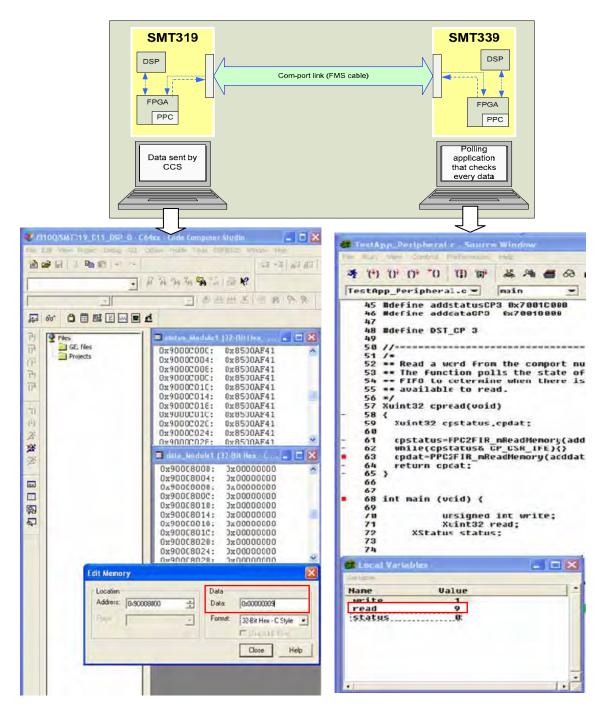

| Figure 17 test scheme                                             | . 31 |

| Figure 18 XMD PowerPC system connexion                            | . 32 |

| Figure 19 memory map without OPB bridge                           | . 33 |

| Figure 20 bus interface without OPB bridge                        |      |

| Figure 21 OPB bus protocol example                                | . 35 |

| Figure 22 IPIF module                                             | . 36 |

| Figure 23 map user port                                           | . 37 |

| Figure 24 system assembly view - ppc2firm core                    | . 38 |

| Figure 25 port ppc2firm                                           | . 38 |

| Figure 26 block diagram ppc2firm                                  | . 40 |

| Figure 27 ppc_wrapper entity                                      | .41  |

| Figure 28 interface between PB and IB                             | . 42 |

| Figure 29 external ports                                          | . 42 |

| Figure 30 conversion big Endian - little Endian                   | . 43 |

| Figure 31 top level entity                                        | . 43 |

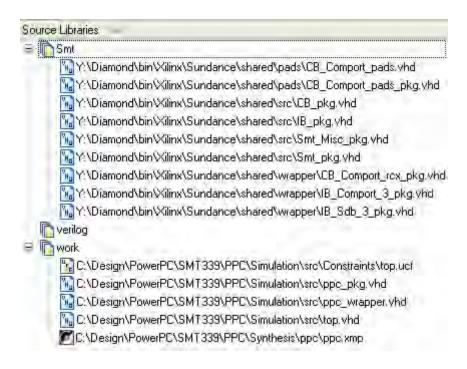

| Figure 32 SMT library                                             |      |

| Figure 33 libraries used                                          |      |

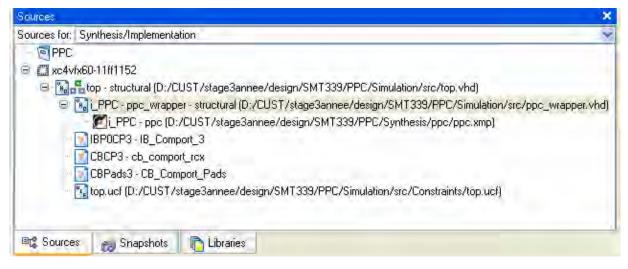

| Figure 34 project hierarchy into ISE                              | . 45 |

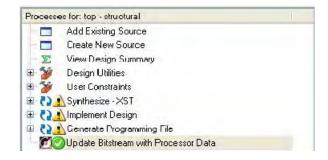

| Figure 35 implementation processes into ISE                       | . 45 |

| Figure 36 update SmtTim.h file                                    |      |

| Figure 37 user application                                        | . 48 |

| Figure 38 test scheme for the com-port link                       | . 48 |

| Figure 39 test com-port link CCS - XMD debugger                   | . 50 |

| Figure 40 polling example                                         |      |

| Figure 41 IP catalog                                              |      |

| Figure 42 PLB top-level block diagram                             |      |

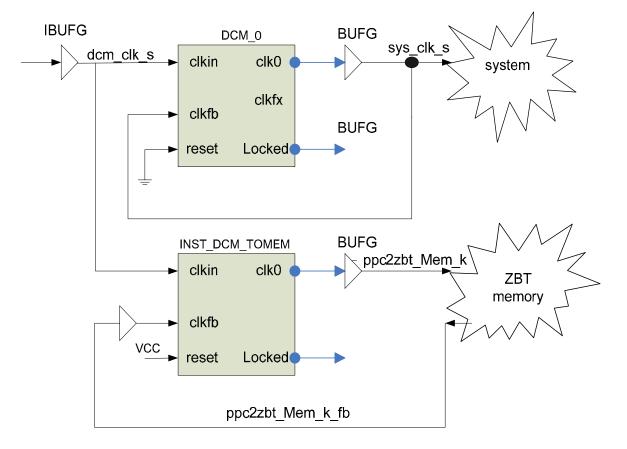

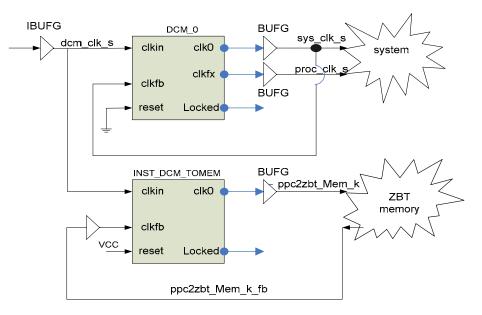

| Figure 43 synchronous memory clocked by FPGA output with feedback |      |

| Figure 44 system assembly view for ZBT design                     | . 57 |

### Sundance Multiprocessor Technology Limited

| 9 |

|---|

| 0 |

| 1 |

| 2 |

| 4 |

| 5 |

| 7 |

| 8 |

| 9 |

| 0 |

|   |

# TABLE

| Table 1 specification                                               | 13 |

|---------------------------------------------------------------------|----|

| Table 2 big Endian byte orderingTable 3 little Endian byte ordering |    |

| Table 4 Software version                                            | 25 |

| Table 5 design memory map                                           | 28 |

| Table 6 program size                                                | 32 |

| Table 7 device utilisation                                          |    |

| Table 8 memory map - ppc2firm                                       | 39 |

| Table 9 description of the signals Comport                          |    |

| Table 10 event block signals                                        |    |

| Table 12 connexion between EMC and ZBT memory                       | 56 |

| Table 13 address bus connexion                                      | 58 |

| Table 14 data bus connexion                                         | 59 |

| Table 15 memory map for the ZBT design                              | 60 |

| Table 16 memory test descrption                                     |    |

| Table 17 memory map global design                                   |    |

# INTRODUCTION

Sundance Multiprocessor Technology Limited is a British firm located in Chesham, to the North-west of London. As shows by its name, this company designs and produces boards, with processors on them, dedicated for high frequency acquisition and data processing application. These boards, built with DSPs and FPGAs, are designed to the Texas Instrument Module standard.

To communicate and synchronise the parallel processing on different targets, DSPs and FPGAs, the designers need methods and tools to fill these requirements. Sundance works in partnership with companies providing high level design tools to ease development of applications for the Sundance's systems. **3L** is a company that offers DIAMOND, a design tool which is optimised for the Sundance products.

Thanks to new technology, FPGAs now provide a hardware/software development target within a single programmable device. An FPGA embedded processor system offers many exceptional advantages compared to typical microprocessors. Because of this, Sundance's customers want to develop applications implementing embedded processors. As yet, Sundance has not provided solutions to implement an embedded processor such as PowerPC and Microblaze into its boards. It needs to develop reference designs providing solutions for its customers and application notes describing every design.

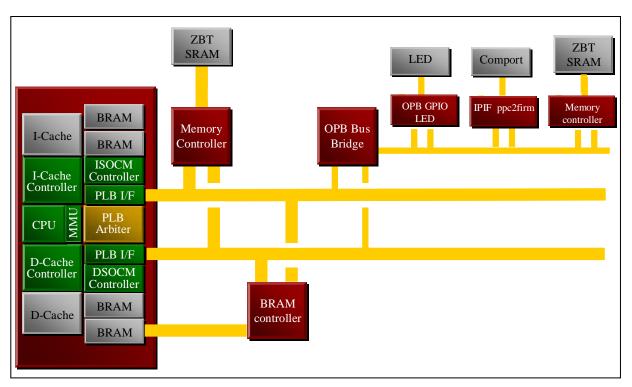

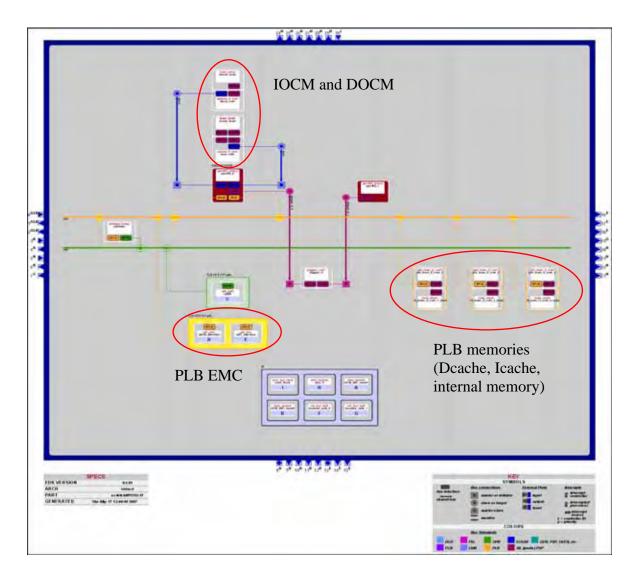

This design was split into three modular designs to make the implementation easier. The first design contained a PowerPC with Sundance communication resources. This design allowed an embedded processor to transfer data to another processor such as a DSP. The second design implemented a PowerPC with an external ZBT memory controller. This design provided 8MB external memory to the processor. The memory controller was connected onto both interconnect buses: On-Chip Peripheral Bus (OPB) and Processor Local Bus (PLB). The last design incorporated every element: external memory, two communication resources, GPIO LED, data On-Chip Memory-Bus, instruction On-Chip Memory-Bus, data-cache side, instruction-cache side and internal memory. Application notes are available to give some information about each phase of the project. Each design is based on the model 3L DIAMOND uses to describe a system (<u>3L Diamond</u>).

### **1** Project description

This chapter contains the aim of this design and its specification.

### 1.1 The main objective

Advances in FPGA technology allow manufacturers to insert more and more peripherals increasing the functionality of this chip into their FPGAs. In the latest FPGAs, you can find trimode Ethernet Media Acess Controller that operates at 10, 100 and 1000 Mb/s, 100 Mb/s to 3,2Gb/s serial transceivers, In Tegrated Endpoint Block for PCI Express Compliance delivering full PCI Express Endpoint functionality, high-speed clock management circuitry, dedicated DSP slices. Also, a wide array of FPGA hard-IP core blocks include embedded processors.

FPGA manufacturers like Xilinx spent a lot of money to promote their embedded systems. For example, Xilinx has been developing a tool to simply implementing Xilinx's IP cores and embedded processors. Thus, a lot of people are very interested by these embedded processors because they can develop a design with both hardware and software application within the same chip.

Sundance's customers are very interested to use the PowerPC. To answer customer demand, Sundance have to support these embedded processors which formed the basis of this application note.

### 1.2 Requirement

This project was split in several applications to make the implementation easier. But the whole of the following specifications should be enforced for every application. All specifications are contained in the **Table 1**.

#### 1.2.1 Processor choice

Sundance works in partnership with Xilinx foundation. Xilinx provides FPGA families that embed two kinds of processors: the Microblaze and the PowerPC. The Microblaze is a soft processor core optimized for Xilinx's FPGA, by contrast, the PowerPC, created by IBM, is a physical processor built into the FPGA silicon, which delivers several advantages. You can find more details about these processors in section that follow.

PowerPC is the architecture of choice in the embedded world. This kind of processor was used on game console such as Nintendo's GameCube and Wii, Sony's PlayStation 3 and Microsoft's Xbox 360 and in the personal computer market like Apple's Macintosh. The PowerPC architecture developed is very famous and the knowledge about this processor is quite important.

Contrary to the Microblaze, the PowerPC architecture is independent of the target and it is built from dedicated silicon. Its implementation into a design does not change the performances of the device.

Although the PowerPC provides features better than the Microblaze, only certain Xilinx FPGA families embed a PowerPC. Despite this, this application note implements a PowerPC because Sundance boards provide both co-design solutions: FPGA-DSP or FPGA-PowerPC. Thus, if the FPGA does not embed a PowerPC, the software application may be developed on the DSP. An application designed for a PowerPC can easily be moved to the Microblaze processor. In fact, these both processors provide the same communication resources. Similarly, IP blocs can be shared between the processor and the same programming language is used.

### 1.2.2 Communication resources

To allow the PowerPC to communicate with another processor such as a DSP, the host or FPGA, it has to implement the Sundance's communication resources. Typically, Sundance FPGAs implement four types of communication resources. These resources are implemented in firmware in the FPGA. The aim of this application note was not to implement all communication resources in the PowerPC. By using 3L DIAMOND the required communication resources are implemented automatically.

The following are types of communication resources:

- > comport

- Sundance digital bus

- global bus

- rocket IO serial link

The Comport link was chosen among other links to connect the PowerPC to another processor for many reasons.

Firstly, the Comport is the simplest of the Sundance communication resources. Its implementation on an FPGA would be easier and quicker than rocket IO links for example.

A basic application was developed allowing a PowerPC to transfer data to another processor. This would be easier to validate and improve it.

The Comport is usually used to download programs to processor TIMs. This method is used by DIAMOND to load boot code into processor TIM. Thus, it was important to implement this link to simplify the development of the DIAMOND PPC software.

The implementation of communication resources follow design guidelines set out by Sundance.

#### 1.2.3 External memory

On Sundance boards, some FPGAs are connected with an external memory. Fast memory is connected to FPGA allowing high speed data storage. Many kinds of memory may be connected with FPGA such as SDRAM, DDR, Flash. But a type of memory used on Sundance board provides interesting features.

Zero-bus turnaround (ZBT) SRAM with no bus latency memory is a synchronous-burst SRAM with a simplified interfaced that fully uses available bandwidth.

ZBT SRAM devices use the full bandwidth because they do not require turnaround cycles. A turnaround cycle is idle cycles between read and write or write and read operation.

An external ZBT memory controller was implemented to connect a ZBT SRAM with the PowerPC. According to PowerPC buses, data rate expected is 40MB/s.

This external memory is used to store data from the PowerPC. Thus, memory controller has to support several accesses like byte, half word (2 bytes) and word (4 bytes). And the memory map should be laid out to follow guidelines set out by DIAMOND. For example, internal memory must precede external memory.

| Peripherals         | External ZBT memory     | Comport link        | PowerPC           |  |

|---------------------|-------------------------|---------------------|-------------------|--|

| Features            | controller              |                     |                   |  |

| Туре                | ZBT - K7N321801M        | Com-port            | PPC 405           |  |

| Clock               | 100MHz                  | 50MHz               | 300MHz            |  |

| width               | 2x18bits (4Mbytes)      | 32bits              | -                 |  |

| Number device       | 2(separate)             | 2(comport 3 et 2) 2 |                   |  |

| Bus interface       | OPB/PLB s               | OPB                 | OPB/PLB           |  |

| Burst mode          | Supported               | -                   | -                 |  |

| Access mode         | 8bits – 16bits – 32bits | -                   | -                 |  |

|                     | read and write          |                     |                   |  |

| mode                | Pipeline                | -                   | -                 |  |

| Implementation      | IP block                | IP block-           | -                 |  |

|                     |                         | connector block     |                   |  |

| Internal memory     | Consecutive             | -                   | 64Kbytes          |  |

| External memory     | Consecutive             | -                   | 8Mbytes           |  |

| instruction-cache   | truction-cache -        |                     | 4Kbytes           |  |

| data asaka          |                         |                     | 416 h + to o      |  |

| data-cache          | -                       | -                   | 4Kbytes           |  |

| Data on-chip        | -                       | -                   | 16Kbytes          |  |

| memory(DOCM)        |                         |                     |                   |  |

| Instruction on-chip | -                       | -                   | 16Kbytes          |  |

| memory(IOCM)        |                         |                     |                   |  |

| Debug port          | -                       | -                   | JTAG              |  |

| Target              | virtex4                 | Virtex2P- virtex4   | Virtex2P- virtex4 |  |

| Sundance board      | SMT339,                 | SMT339,             | SMT339,           |  |

|                     | SMT398,                 | SMT398,             | SMT398,           |  |

|                     | SMT145FX                | SMT145FX,           | SMT145FX,         |  |

|                     |                         | SMT338VP            | SMT338VP          |  |

### Table 1 specification

The following scheme describes the design expected for this application note.

Figure 1 design expected

### 1.3 Background

This paragraph describes blocks implemented such as Sundance resources, external memory controller and PowerPC.

### 1.3.1 Embedded processor

As described before, there are two types of embedded processors. Hard and soft core.

A "soft" processor is built using the FPGAs general-purpose logic. The "soft" processor is described in a Hardware Description Language (HDL) or netlist. Unlike the hard processor, processor such as Microblaze must be synthesized and fit into the FPGA fabric.

Xilinx produces FPGA families that embed a physical processor core into the FPGA silicon. A processor built from dedicated silicon is referred to as a "hard" processor. Such is the case for the PowerPC. 405 inside the Xilinx Virtex-II Pro and Virtex-4 families.

Figure 2 PowerPC hard processor

In both soft and hard processor systems, the local memory, processor busses, internal peripherals, controllers, and memory controllers must be built from the FPGA's general-purpose logic.

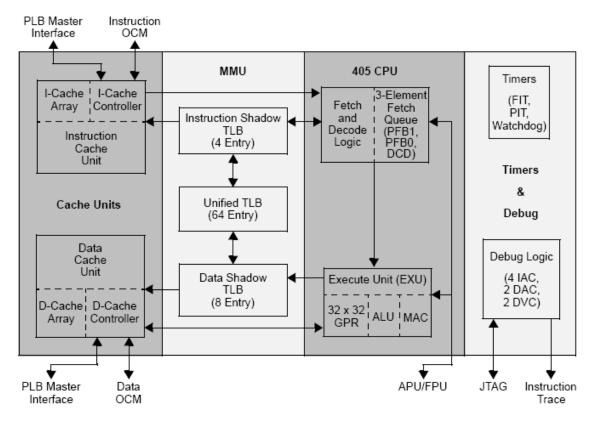

The PowerPC 405 processor is a 32-bit implementation of the PowerPC embedded environment architecture that is derived from the PowerPC architecture. Specifically, the PowerPC 405 processor is an embedded PowerPC 405D5 (for Virtex-II Pro) or 405F6 (for Virtex-4) processor core. The term processor block is used throughout this document to refer to the combination of a PPC405, on-chip memory logic (OCM), an APU controller (Virtex-4 only), and the gasket logic and interface.

The processor core consists of a 5-stage pipeline, separate instruction and data cache units, virtual memory management unit (MMU), three timers, debug, and interface to other functions. **Figure 3** illustrates the logical organization of the PPC405Fx.

Figure 3 PowerPC405Fx block diagram

The PowerPC is designed along RISC principles, and allows for a superscalar implementation. The PPC405 supports both big-endian and little-endian byte ordering, but by default, the PowerPC Architecture is Big Endian. In Big Endian, the MSB of an instruction word is assumed to be at the lowest address.

| LSB  |      |      | MSB  |

|------|------|------|------|

| 0x03 | 0x02 | 0X01 | 0x00 |

| MSB  |      |      | LSB  |

|------|------|------|------|

| 0x03 | 0x02 | 0X01 | 0x00 |

Table 2 big Endian byte ordering

Table 3 little Endian byte ordering

In a Little Endian program the same instruction is arranged with the least significant byte (LSB) of the instruction word at the lowest numbered address.

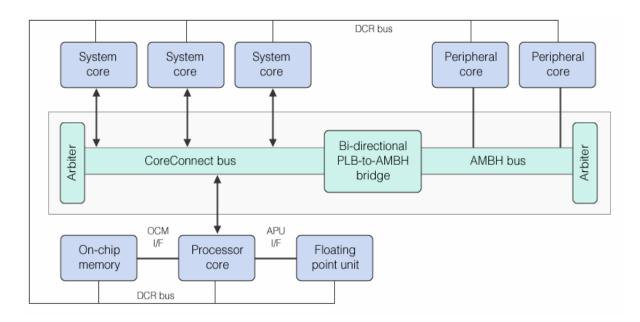

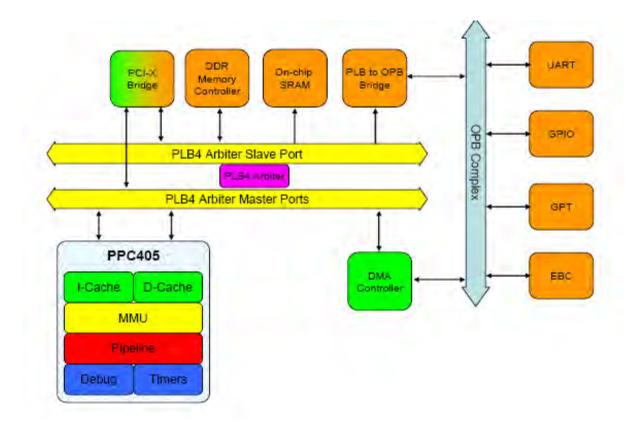

CoreConnect<sup>™</sup> is an IBM-developed on-chip bus-communications link that enables chip cores from multiple sources to be interconnected to create entire new chips. The CoreConnect technology eases the integration and reuse of processor, system and peripheral cores within standard product platform designs to achieve overall greater system performance. The CoreConnect bus architecture includes the Processor Local Bus (PLB), the On-chip Peripheral Bus (OPB), a bus bridge, two arbiters, and a Device Control Register (DCR) bus.

Figure 4 CoreConnect bus architecture

The 64-bit Processor Local Bus (PLB) consists of a bus control unit, a watchdog timer, and separate address, write and read data path units with a three-cycle-only arbitration feature. It contains a DCR slave interface to provide access to its bus error status registers. It also contains a power-up reset circuit to insure that a PLB reset is generated if no external reset has been provided. The PLB consists of a central bus arbiter, the necessary bus control and gating logic, and all necessary bus OR/MUX structures. The PLB provides the entire PLB bus structure and allows for direct connection for up to 16 masters and 16 slaves.

The On-chip Peripheral Bus (OPB) implements a 32-bit address bus and a separate 32-bit data bus. Transaction widths can be full-word, half-word, or byte-size. The bus supports 8-, 16-, and 32-bit wide device interfaces (aligned on the left-most byte).

It's a synchronous bus, data transactions can take a single cycle (for matched clocks), and burst operations are supported. Designed to support slower peripherals, the OPB is implemented as a straightforward multimaster, arbitrated bus.

The DCR bus provides an alternative path to the system for setting the individual device control registers. With it, the host CPU can set up the device-control-register sets without loading down the main PLB. This bus has a single master, the CPU interface, which can Read or Write to the individual device control registers. The bus employs a ring implementation to connect the CPU interface to the devices, which are addressed via a 10-bit address bus. A separate 32-bit data bus transfers register data. This is a synchronous bus.

A bridge is a synthesizable core that permits transfers of code and data between two different buses as such the Advanced Microcontroller Bus Architecture (AMBA) advanced high-performance bus (AHB) and the CoreConnect PLB (see the **Figure 4**).

A typical system-on-a-chip (SOC) implementation based on the PowerPC 405 CPU and CoreConnect, uses a three level bus structure for system level communication, configuration and control functions. High bandwidth memory and system interfaces are tied to the PowerPC 405 Core via the Processor Local Bus (PLB). Less demanding peripherals share the On-chip Peripheral Bus (OPB) and communicate to the PLB through the OPB bridge.

This three level bus architecture provides common interfaces for the IP cores. This application note is according to this architecture. **Figure 5** illustrates a representative SOC configuration.

### Figure 5 PowerPC405 CPU and CoreConnect based SOC example

#### 1.3.2 External ZBT memory

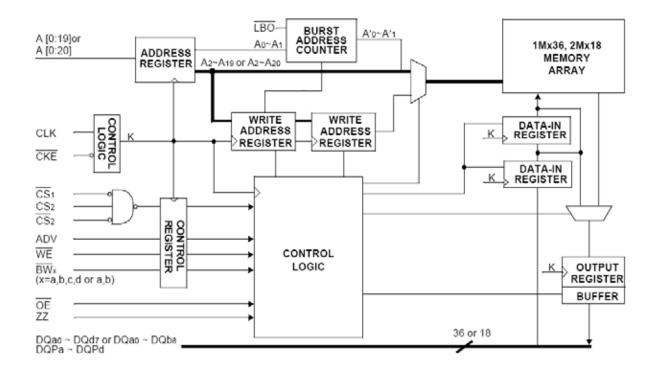

This design was developed on the SMT339. On this board, 8 Mbytes of ZBT SRAM is provided as a FPGA memory resource. The memory is based on two separate Samsung K7N321801M-20 devices which are each 2M by 18-bit devices, allowing independent access of each device.

The K7N321801M is Synchronous Static SRAMs. The N*t*RAMTM, or No Turnaround Random Access Memory utilises all the bandwidth in any combination of operating cycles.

Figure 6 ZBT memory block diagram

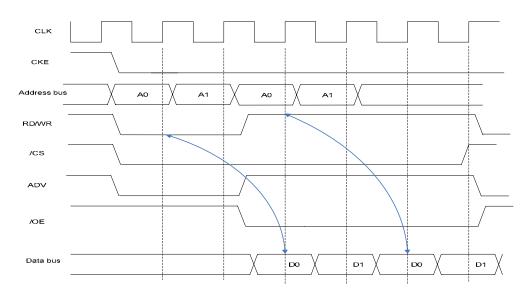

The following figure explains the timing feature for this memory.

Figure 7 timing feature of the ZBT memory

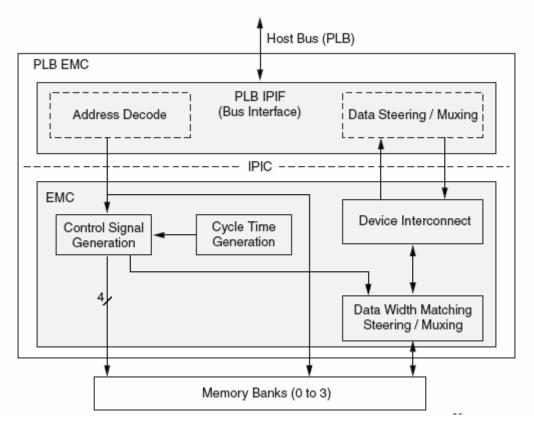

Xilinx provides external memory controllers (Xilinx EMC PLB). These modules support data transfer between the Processor Local Bus or On-chip Peripheral Memory and external synchronous and asynchronous memory devices. These kinds of controller receive control signals from the PLB or OPB to read and write to external memory devices.

The PLB/OPB EMC supports PLB data bus widths of 8, 16, 32, 64bits and OPB data bus widths of 8,16,32 bits, and memory subsystem widths of 8, 16, 32 (64bits for PLB). However, this ZBT control does not support sleep mode, burst mode (memory mode), parity checking or parity generating. "This controller does not support burst mode" means that the user can read and write to the ZBT memory in burst mode but the burst sequence provides by the memory is not used; a signal is used to load a new external address or increment the initial burst counter. In this case, the ZBT memory loads a new external address every read or write access.

Some features of the OPB/PLB EMC can be parameterized such as number of separate memory banks, memory type (synchronous or asynchronous), data width of each memory bank, pipeline delay of each memory, read and write access times for each memory bank, enabling of data-width matching per memory bank, enabling burst support and enabling negative edge IO registers enabling of PLB burst and cache line transaction support. The descriptions of every OPB/PLB EMC parameters are described in the following section.

### 1.4 Test bench configuration

This section explains hardware and software required for this application.

### 1.4.1 Hardware set up

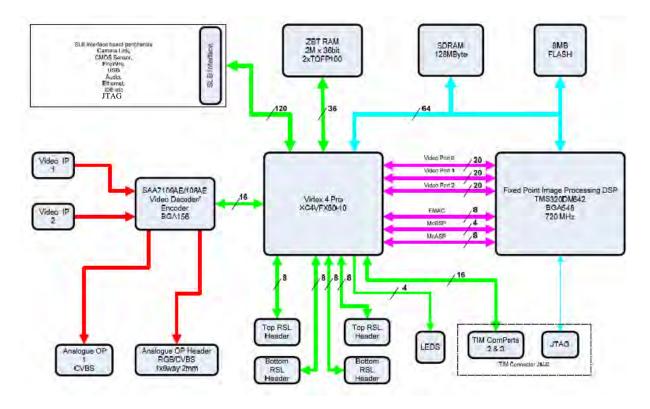

This application note was developed on the <u>SMT339</u>. This board is a dedicated high speed image processing module for use in a wide range of image analysis systems. The module can be plugged into a standard TIM single width slot and can be accessed by either a standard Comport, or Rocket Serial Link (RSL) Interface. The image processing engine is based upon the 'Texas Instruments' TMS320DM642 Video Digital Signal Processor. It is fully software compatible with C64x using Code Composer Studio.

The DM642 runs at a clock rate of 720MHz. It features two levels cache based architecture. There are 16K Bytes of level one program cache (Direct mapped), 16K Bytes of level one data cache (2-Way Set-Associative) and 256K Bytes of level two cache that is shared program and data space (Flexible RAM/Cache Allocation). TheDM642 can perform 4, 16 x 16 Multiplies or 8, 8 x 8 Multiplies per clock cycle.

A powerful Vitrex-4 FPGA (XC4VFX60-11) is used onboard as the FPGA processing unit for image data. 8 Mbytes of ZBT SRAM is provided as a FPGA memory resource. Processing functions such as Colour Space Conversion (CSC), Discrete Cosine Transforms (DCT), Fast Fourier Transforms (FFT) and convolution can be implemented, without using any of the DSP's resources. The Virtex 4FX60 has 2 Power PC hardware cores that can be incorporated into this design.

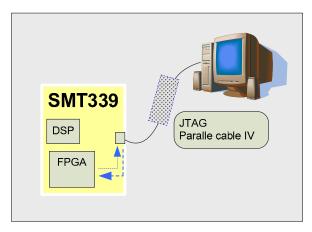

The basic block diagram of the SMT339 and its components is illustrated Figure 9.

Figure 8 SMT339 diagram block

There are two separate JTAG chains on the SMT339 module. One allows the DSP chain to be accessed while the other allows the Virtex 4 to be configured. The last one was used to debug the PowerPC with Xilinx Micro-Processor debug (XMD).

The <u>SMT 319</u> was connected to the SMT339 via comport link to print the result on the host.

The SMT319 is a Graphics and Imaging Module based on Texas Instruments (TI) highperformance, TMS320C6414 digital signal processor (DSP), that allows original equipment manufacturers (OEM) designers to easily capture, process and display images without any host computer involvement and as an embedded solution if necessary.

SMT319 is suitable for a wide range of image processing applications including, graphics, rendering of pictures and general-purpose display sub-systems in larger multiDSP processing systems. This solution is supported on major platforms like PCI, CPCI, PXI and VME.

The module also includes a Xilinx Virtex-II FPGA, which is configured to provide "C4x" style Com-Ports, or alternatively the Sundance Digital Link (SDL), a TIM compatible enhanced global bus, two Sundance High Speed Bus (SHB) and other control functions.

#### 1.4.2 Software set up

To simplify the design process, Xilinx offers several sets of tools. The Xilinx Embedded Development Kit (<u>EDK</u>) is a suite of tools and IP that allows to design a complete embedded processor system for implementation in a Xilinx Field Programmable Gate Array (FPGA) device.

EDK includes XPS and SDK software. Xilinx Platform Studio (XPS) is the development environment or GUI used for controlling the hardware and software development of the embedded processor system.

Software Development Kit (SDK) is an integrated development environment, complimentary to XPS, that is used for C/C++ embedded software application creation and verification. SDK is built on the Eclipse<sup>™</sup> open-source framework.

The Integrated Software Environment (ISE) is the foundation for Xilinx FPGA logic design. Because FPGA design can be an involved process, Xilinx has provided software development tools that allow the designer to circumvent some of this complexity. Various utilities such as constraints entry, timing analysis, logic placement and routing, and device programming have all been integrated into ISE.

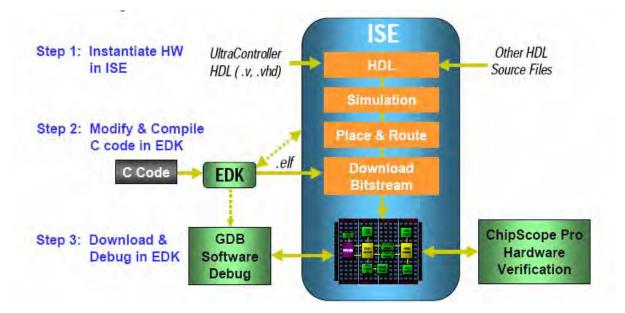

Figure 9 Simplified ISE / EDK Design Flow

Like Xilinx, Texas Instrument provides several sets of tools. Code Composer Studio<sup>™</sup> integrated development environment includes host tools and target software that slashes development time and optimizes the performance for all real-time embedded DSP applications.

The CCStudio IDE includes DSP/BIOS support, real-time analysis capabilities, debugger and optimization tools, C/C++ Compiler, Assembler, Linker, integrated CodeWright editor, visual project manager, and a variety of simulators and emulation drivers.

Figure 10 development cycle with Code Composer Studio

Software required for this reference design is described in the following table:

| Software             |     | version |

|----------------------|-----|---------|

| ISE                  | ISE | 9.1 SP3 |

| <u>EDK</u>           | Ś   | 9.1 SP2 |

| Code Composer Studio |     | 3.3     |

Table 4 Software version

### 1.5 Design implementation

The main objective explained and every specification defined, the next step is the implementation of this application.

### 1.5.1 PowerPC block

This paragraph demonstrates process of creating and testing a PowerPC system design using the Embedded Development Kit (EDK).

### 1.5.1.1 Overview

This design implemented the PowerPC block and General Purpose Input/Ouput (GPIO). This peripheral was used to flash LEDs on the board. The PowerPC was running at 100MHz like its communication links. By a basic example, this design allowed users to understand the PowerPC architecture and use Xilinx's software and hardware. In this example, the design flow was generated by EDK.

### 1.5.1.2 Constraints

According to the requirement, all system was running at 100 MHz to make easier the implementation. This constraint can be checked in the MHS file. The Microprocessor Hardware Specification (MHS) file describes the embedded processor: either the soft core MicroBlaze processor or the hard core PowerPC, peripherals and associated address spaces, buses and overall connectivity of the system.

The MHS file is a readable text file that is an input to the Platform Generator; the hardware system building tool. Conceptually, the MHS file is a textual schematic of the embedded system.

For the Sundance board, the bitgen file needs to be changed. It contains every setting for JTAG configuration. By default, the device is synchronised to the clock provided by JTAG.

This option specifies the start-up sequence for the device synchronisation. But Sundance's TIMs need clock system to download the bitstream before connecting to the JTAG. Thus, the default clock startup needs to be replaced by the clock provided in the FPGA device: "-g StartUpClk:CCLK".

If you don't change this parameter, you cannot download the bitstream into the FPGA with the Sundance package (SMT6001).

For design entry in VHDL, only a few constraint options can be embedded in the source code. In this case, designers have the option to use a UCF. User constraint files allow designers to manually control some of the following attributes in a FPGA design: pin and node assignments, slew rate control, fit options, input pin characteristics, initial register state, global clock use. In this design, the user constraint file contains only five pin assignments: Clk, Rst, LED(0 to 2).

This implementation includes both hardware and software. In fact, this design needs components such as PLB controller, BRAM...and a software application as well.

### **1.5.1.3** Hardware implementation

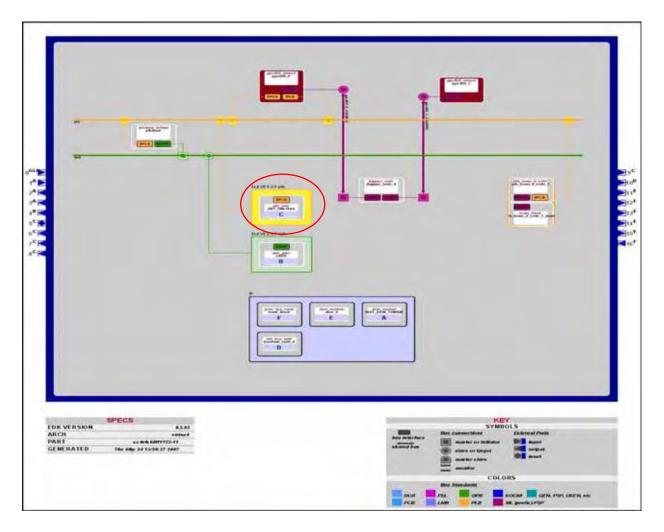

Figure 12 shows the system assembly view created with the Base System Builder.

| P O<br>L P                                | Filters<br>• • • Bus Interface O Ports |                | ≧v Filters (Applied | i)         |

|-------------------------------------------|----------------------------------------|----------------|---------------------|------------|

| BB                                        | Name                                   | Bus Connection | IP Type             | IP Version |

|                                           | і <u>в</u>                             |                | ppc405_virtex4      | 1.01.a     |

| <u>□</u> +•-⊳́                            | ⊕                                      |                | ppc405_virtex4      | 1.01.a     |

| ┝──┼┼┼┼──                                 | 🚋 - 🗢 plb                              |                | plb_v34             | 1.02.a     |

|                                           | 🗐 🗢 opb                                |                | opb_v20             | 1.10.c     |

| <del>       </del>                        | 🗊 🗢 jtagppc_0                          |                | jtagppc_ontlr       | 2.00.a     |

|                                           | 😥 🥯 reset_block                        |                | proc_sys_reset      | 1.00.a     |

| 🧅 🎍 🗕 — — — — — — — — — — — — — — — — — — | 🗊 🗢 plb2opb                            |                | plb2opb_bridge      | 1.01.a     |

| <u> </u>                                  | 🗊 🗢 LEDS                               |                | opb_gpio            | 3.01.Б     |

| ←                                         | 🗊 🗢 plb_bram_if_cntlr_1                |                | plb_bram_if_cntl    | r1.00.Б    |

| -                                         | 🗊 🗢 plb_bram_if_cntlr_1_bran           | r -            | bram_block          | 1.00.a     |

|                                           | 😥 🧼 dam_0                              |                | dcm_module          | 1.00.c     |

#### Figure 11 system assembly view

Both PowerPC cores were implemented: ppc405\_0 and pp405\_1. But only the ppc405\_0 was used. This basic example includes both CoreConnect bus architecture the Processor Local Bus (PLB) and the On-chip Peripheral Bus (OPB). The ports tab gives further information about the connectivity between the blocks.

| Name                          | Net                    | Dire       | ection   ( | Class | Sensitivity | Range | Frequency | Reset Polarity | IP Type          | IP Version |

|-------------------------------|------------------------|------------|------------|-------|-------------|-------|-----------|----------------|------------------|------------|

| 😑 🥯 External Ports            |                        |            |            |       |             |       |           |                |                  |            |

| fpga_0_LEDS_GPl0              | fpga_0_LEDS_GPI0_d_out | <b>v</b> 0 | ~          | ~     |             | [0:2] |           |                |                  |            |

| sys_clk_pin                   | dem_elk_s              | ✓          | 🗸 🗸 🗸      | CLK 🔽 |             |       | 100000000 |                |                  |            |

| sys_rst_pin                   | sys_rst_s              | <b>v</b> I | 🗸 F        | RST 🔽 |             |       |           | 0 💌            |                  |            |

| 🗐 🗢 ррс405_0                  |                        |            |            |       |             |       |           |                | ppc405_virtex4   |            |

| 🕀 🗢 ррс405_1                  |                        |            |            |       |             |       |           |                | ppc405_virtex4   | 1.01.a     |

| 🖨 🗢 plb                       |                        |            |            |       |             |       |           |                | plb_v34          | 1.02.a     |

| PLB_Clk                       | sys_clk_s              | ~          | C          | :LK   |             |       |           |                |                  |            |

| SYS_Rst                       | sys_bus_reset          | ~          |            |       |             |       |           |                |                  |            |

|                               | No Connection          | ✓ 0        |            |       |             |       |           |                |                  |            |

|                               | No Connection          | ✓ 0        | 11         | NTE   | EDGE_RI     |       |           |                |                  |            |

| 🖨 🥯 opb                       |                        |            |            |       |             |       |           |                | opb_v20          | 1.10.c     |

|                               | sys_clk_s              | ~          | C          | :LK   |             |       |           |                |                  |            |

|                               | sys_bus_reset          | ~          |            |       |             |       |           |                |                  |            |

| ı∎ 🗢 jtagppc_0                |                        |            |            |       |             |       |           |                | jtagppc_ontlr    | 2.00.a     |

| 🗄 🥯 reset_block               |                        |            |            |       |             |       |           |                | proc_sys_reset   |            |

| 🕀 🗢 plb2opb                   |                        |            |            |       |             |       |           |                | plb2opb_bridge   |            |

| $\blacksquare \bigcirc LEDS$  |                        |            |            |       |             |       |           |                | opb_gpio         | 3.01.Б     |

| 😑 🗢 plb_bram_if_cntlr_1       |                        |            |            |       |             |       |           |                | plb_bram_if_cntl |            |

| 📮 🗢 plb_bram_if_cntlr_1_bran. |                        |            |            |       |             |       |           |                |                  | 1.00.a     |

| 표 🥯 dcm_0                     |                        |            |            |       |             |       |           |                | dcm_module       | 1.00.c     |

Figure 12 blocks connexions

Blocks connexions allowed user to check the frequency, the reset polarity and every connexion between blocks. It is the graphic interface of the MHS file.

The following table shows the memory map for this design as created by Base System Builder.

| Device         | Address    |            | Size | Comment    |

|----------------|------------|------------|------|------------|

|                | Min Max    |            |      |            |

| PLB_BRAM_CNTLR | 0xFFFFC000 | 0xFFFFFFFF | 16K  | PLB Memory |

| OPB_GPIO       | 0x40000000 | 0x4000FFFF | 64K  | LED output |

| PLB2OPB        | 0x40000000 | 0x4000FFFF | 64K  | Bridge     |

#### Table 5 design memory map

It is important to check the address of every component. In fact, a peripheral can be controlled by the PowerPC, if it is part of PowerPC address range.

Figure 14 describes hardware component implemented by the wizard.

|                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>1</b> 476 |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| SPECS<br>EDK VERSION 8.8.8<br>ARCH voteor<br>PART xc-dwisemertS3-re<br>GENERATED The May 17 15-48.34 2007 | SYMBOLS<br>Symbols<br>Symbols<br>Stared Sur<br>Stared Sur<br>Sta |              |

Figure 13 Block diagram PowerPC - GPIO

After that the hardware had been completely specified in the MHS file, Platform Generator was able to run. Platform Generator elaborates the MHS file into a hardware system consisting of NGC files that represent the processor system. Then it can generate a netlist and create the bit file.

#### **1.5.1.4** Software implementation

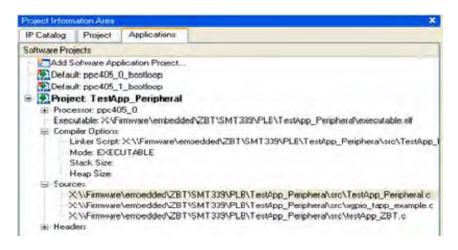

The next step is defining the software design. There are two major parts to software design, configuring the Board Support Package (BSP) and writing the software applications. The configuration of the BSP includes the selection of device drivers and libraries.

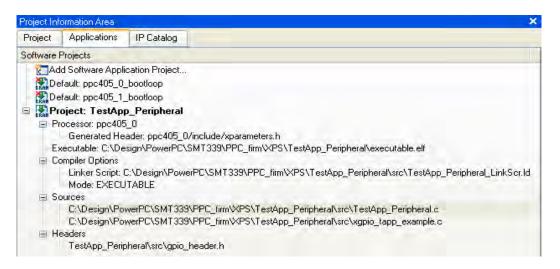

Software application code development for this design is shown in Figure 15.

Figure 14 application tab

The Base System Builder (BSB) generates a sample application which tests a subset of the peripherals included in the design.

Both sources code TestApp\_Peripheral.c and xgpio\_tapp\_example.c were added to this project. They were generated by BSB. This application set the Led to high one following the other. These sources code were compiled using the GNU GCC Compiler.

The compiled software routines are available as an Executable Format (ELF) file. The ELF file is the binary ones and zeros that are run on the processor hardware.

| ×     | LibGen Done.<br>powerpc-eabi-gcc -02 TestApp_Peripheral/src/TestApp_Peripheral.c TestApp_Peripheral/src/xgpio_tapp_example.c -o TestApp_Peripheral/executable.elf \<br>-W1,-T -W1,TestApp_Peripheral/src/TestApp_Peripheral_LinkScr.ld -g -I./ppc405_0/include/ -ITestApp_Peripheral/src/ -L./ppc405_0/lib/ \<br>powerpc-eabi-size TestApp_Peripheral/executable.elf |             |             |             |     |                                               |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-----|-----------------------------------------------|--|--|--|

| wopuj | text<br>3646<br>Done!                                                                                                                                                                                                                                                                                                                                                | data<br>332 | bss<br>2120 | dec<br>6098 | hex | filename<br>TestApp_Peripheral/executable.elf |  |  |  |

### Figure 15 XPS output widows - software compiled

#### **1.5.1.5** Test and validation

After that the hardware and software designs were completed, device can be configured. The Host was connected to the target board via the Parallel-JTAG cable IV.

The figure below shows the test scheme.

Figure 16 test scheme

The bitstream was downloaded by SMT6001 package. The main program of the SMT6001 package, the Flash Programming Utility, manages the Flash ROMs on Sundance TIMs. The Flash Programming Utility uses Texas Instruments' Code Composer<sup>™</sup> to allow the user to analyse the contents of a ROM and program new data. For added security, the Flash Programming Utility will also allow the user to erase the ROM completely.

Both files are generated by EDK: PPC.bit and download.bit. For software downloading: software can be initialized into the bitstream if it fits inside FPGA internal block RAM (BRAM) memory. Else the software debug tools can be used, such as the XPS Software Development Kit (SDK), to download a program to the board.

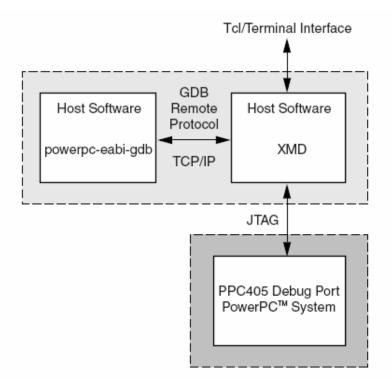

Download.bit file merges the FPGA bitstream and ELF files into a single bitstream file. When this bitstream is downloaded into the FPGA, application runs in standalone after a reset board. Opposed to PPC.bit file that only configures the device. This bitstream is used to debug the software directly via the JTAG PPC connections. GDB connects to the PowerPC core through the JTAGPPC and the Xilinx Microprocessor Debug (XMD) engine utility as shown in **Figure 18**. XMD is a program that facilitates a unified GDB interface and a TCL (Tool Command Language) interface for debugging programs and verifying microprocessor systems.

Figure 17 XMD PowerPC system connexion

This design was validated with these both methods. Before starting the next design, it was important to check features and the resources used by this application.

This design used 4 percents slices into the FPGA. Overview about the embedded processor shows both PowerPC implemented used no resource. That is according to the paragraph describing the embedded processor into FPGA. Indeed, this kind of processor is built from dedicated silicon. Thus, its implementation "doesn't use" FPGA resources.

The following **Table 6** explains the program size.

| Text(Kb) | Data | bss  | dec  | hex  |

|----------|------|------|------|------|

| 3646     | 332  | 2120 | 6098 | 17d2 |

Table 6 program size

| Post Synthesis Device Utilisation |      |           |         |  |

|-----------------------------------|------|-----------|---------|--|

| Resource Type                     | Used | Available | Percent |  |

| Slices                            | 1073 | 25280     | 3       |  |

| Slice Flip flops                  | 1024 | 50560     | 1       |  |

#### Table 7 device utilisation

More than 3 percents slices were used by the PLB controller and the PLB/OPB bridge. Thus, to optimise the resources used by a design, it would be more interesting to implement every peripheral onto the PLB bus.

Just to check this remark, a design without OPB bus interface was created. **Figure 19** shows the memory map and components attached to the PLB.

| Processor: PPC 405<br>Processor clock frequency: 100.000000 MHz<br>Bus clock frequency: 100.000000 MHz<br>Debug interface: FPGA JTAG<br>On Chip Memory : 16 KB<br>The address maps below have been automatically assigned. You can modify them using the<br>editing features of XPS. |                                       |                              |                     |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------|---------------------|--|--|--|

|                                                                                                                                                                                                                                                                                      |                                       |                              |                     |  |  |  |

| -<br>PLB Bus : PLB_V                                                                                                                                                                                                                                                                 | 34 Inst. name: plb /                  | Attached Compor              | ients:              |  |  |  |

| PLB Bus : PLB_V<br>Core Name                                                                                                                                                                                                                                                         | 34 Inst. name: plb /<br>Instance Name | Attached Compor<br>Base Addr | ients:<br>High Addr |  |  |  |

| _                                                                                                                                                                                                                                                                                    |                                       |                              |                     |  |  |  |

Figure 18 memory map without OPB bridge

The following Figure 20 explains bus interfaces. None OPB bus was implemented.

| P        | Filters       Filters       Image: Second state       Image: Second sta |                       |                  |            |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|------------|--|--|

| B        | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Bus Connection</b> | IP Type          | IP Version |  |  |

| 😐 🖓 🔶    | 🗐 🗢 ррс405_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       | ppc405_virtex4   | 1.01.a     |  |  |

| ÷-÷      | ₽                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       | ppc405_virtex4   | 1.01.a     |  |  |

|          | 庄 🗢 plb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       | plb_v34          | 1.02.a     |  |  |

| <u> </u> | 🕀 🗢 jtagppc_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       | jtagppc_cntlr    | 2.00.a     |  |  |

|          | 🕀 🧼 reset_block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       | proc_sys_reset   | 1.00.a     |  |  |

|          | <u> <u> </u> <u> </u> <u> </u> <u> </u> <u> </u> <i> </i></u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       | plb_gpio         | 1.00.Б     |  |  |

| ←        | 🕞 🧼 plb_bram_if_cntlr_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       | plb_bram_if_cntl | г1.00.Б    |  |  |

| <b>-</b> | 🕀 🧼 🗩 plb_bram_if_cntlr_1_bran                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | c .                   | bram_block       | 1.00.a     |  |  |

|          | 🕀 🧼 dcm_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       | dcm_module       | 1.00.c     |  |  |

Figure 19 bus interface without OPB bridge

Only one percent slices was used by this design. This feature is quite important when the area is critical.

### 1.5.2 Comport link implementation

The first design allowed you to create and test a PowerPC system design using the Embedded Development Kit (EDK). In this section, the Comport link was implemented to improve the previous design. The first step defined the requirements.

#### 1.5.2.1 Overview

This design implemented an external peripheral: Comport. The Comport was instantiated like an IP core. A Xilinx's module was used to provide an interface between the OPB bus and the Comport IP core. This design was exported to ISE for the Comport block integration. Indeed, ISE describes every step of the design flow and control the hardware implementation in the FPGA. The Comport link should transfer data to 20MB/s. Every bus and PowerPC had to run at 100MHz according to the specifications.

#### 1.5.2.2 Constraints

The Comport link must be implemented according to Sundance concept of view. All of the Sundance TIMs provide mechanisms to transfer data between modules. The mechanisms are implemented on the TIMs using FPGAs.

The FPGA (Field Programmable Gate Array) is a device that can be configured by software to implement hardware functions. Sundance TIMs use FPGAs to create peripheral devices such as Comports.

Before a TIM can access the mechanisms that will allow it to communicate with other modules, the DSP must load the FPGA with appropriate firmware. This firmware is held in the FPGA data segment of the flash, and will be installed in the FPGA each time the bootloader executes.

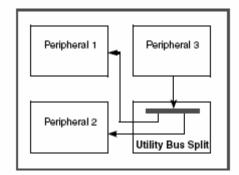

Sundance uses modularity in its designs to improve reusability and maintainability. This approach creates a number of blocks which are used to create the firmware. The role of the firmware is to allow these peripherals to exchange data.

The FPGA is connected to the peripherals via physical wires and these peripherals may be zero or more processors or connectors or other components on the module.

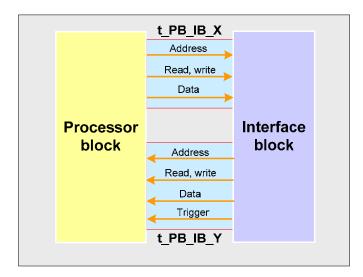

The firmware includes **processor blocks**, **interface blocks**, and **connector blocks**. All blocks are interconnected with pre-defined signals. The connector and processor blocks are connected to the physical pins of the FPGA. This is a standard case of figure. Some modules do not have a processor connected to the FPGA. Usually the firmware for these modules makes use of the standard connector blocks, but the processor and interface blocks may be replaced by a custom controller block.

The next section explains how the Comport link was implemented.

#### 1.5.2.3 Hardware implementation

One of the key advantages of building an embedded system in an FGPA is the ability to include customer IP and interface that IP to the processor. The processor system by EDK is connected by OPB and/or PLB bus, so this custom peripheral: Comport, must contain a set of bus ports that is compliant to OPB or PLB protocol.

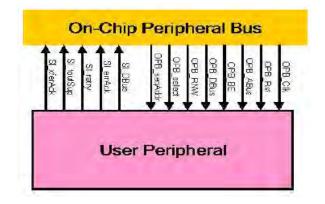

To connect the custom peripheral, Comport, to the PowerPC, the IP core must be attached the system OPB or PLB bus as shown the **Figure 21**.

Figure 20 OPB bus protocol example

Meaning the top-level module of the custom peripheral must contain a set of bus ports that is compliant to OPB or PLB protocol. Another constraint adds to this one.

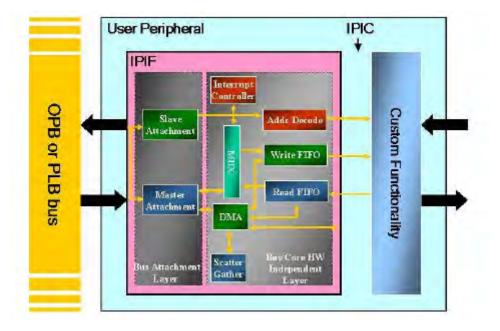

To use the custom peripheral in XPS, the peripheral must be stored in a place (directory structure) that is accessible by various EDK tools; and it must have the correct Platform Specification Format interface files: MPD and PAO files. But Xilinx provides Intellectual-Property Interface (IPIF) library to implement common functionality among various processor peripherals.

Both OPB/PLB IPIF are designed to provide a bidirectional interface between a user IP core and the IBM OPB or PLB Bus.

The back end interface standard, the Xilinx IPIC, is common in most aspects between IPIF modules in various versions for the OPB and the PLB for the features supported. This allows IP blocks using the IPIC to be adapted for either the OPB or the PLB. **Figure 22** shows a block diagram of the OPB IPIF.

Figure 21 IPIF module

According to the specification, the custom peripheral was connected to the OPB bus. The IPIF was generated by "Create and Import Peripheral Wizard" functionality. It was called "ppc2fir". It means PowerPC to firmware. The wizard automatically created corresponding OPB peripheral templates to add the custom peripheral. Two HDL template files were generated: peripheral top-level and user-logic HDL templates.

The top-level file, ppc2fir.vhd, is the template file for the peripheral's top design entity. It configures and instantiates the corresponding IPIF unit in the way you indicated in the wizard GUI and connect it to the stub user logic where the user logic should get implemented.

The recommended design using wizard is added the user port mapping in the top-level file and incorporated the custom IP functionality in the file user\_logic. In this case, the software can access to the peripheral thanks to the software addressable registers. It means the user logic component of the peripheral has registers that are addressable through software. But the Comport IP was not implemented according to this recommendation.

The Comport implementation needed high constraint onto these control signals. It was easier to define these constraints in ISE. This software describes every step of the design flow allowing designers to check every step to see if the constraints were met. So the Comport IP functionality was not implemented in the user\_logic file.

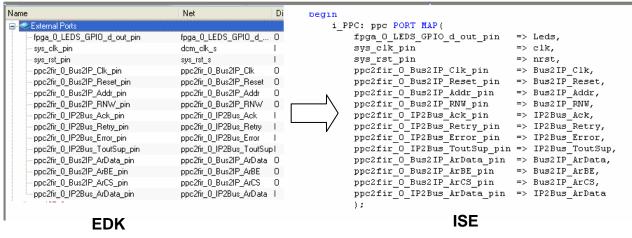

Indeed, the user port mapping was just added in the top-level file as shown **Figure 23** and the user\_logic component instantiation was deleted. The ppc2firm core was connected to the Comport link in Xilinx ISE.

```

port

(

-- ADD USER PORTS BELOW THIS LINE -----

--USER ports added here

Bus2IP Clk

: out std logic;

Bus2IP Reset

: out std logic;

Bus2IP Addr

: out std logic vector(O to C AWIDTH-1);

Bus2IP RNW

: out std logic;

IP2Bus Ack

: in std logic;

IP2Bus Retry

: in std logic;

IP2Bus Error

: in std logic;

IP2Bus ToutSup

: in std logic;

Bus2IP ArData

: out std logic vector (O to C MAX AR DWIDTH-1);

Bus2IP ArBE

: out std logic vector(O to C MAX AR DWIDTH/8-1);

Bus2IP ArCS

: out std logic vector(O to C NUM ADDR RNG-1);

: in std logic vector (O to C MAX AR DWIDTH-1);

IP2Bus ArData

-- ADD USER PORTS ABOVE THIS LINE ------

```

#### Figure 22 map user port

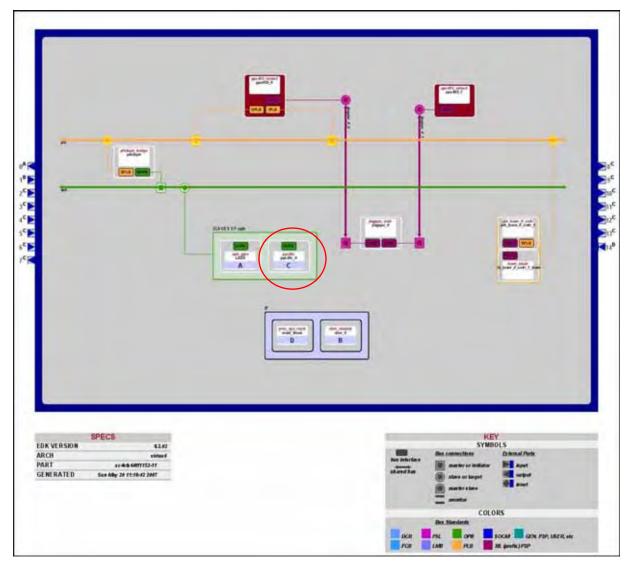

Figure 24 shows the system assembly view in EDK implementing the "ppc2firm" core.

| Project Informa                | tion Area    |              | × |       |      | •        | Filters         |             |                       |                  |            |

|--------------------------------|--------------|--------------|---|-------|------|----------|-----------------|-------------|-----------------------|------------------|------------|

| IP Catalog                     | Project      | Applications |   | 0     | Р    |          | 💿 Bus Interface | O Ports     | O Addresses           | Prion F €        | ilters     |

| •                              |              |              |   | P     | Ĺ,   | Nar      | ne              |             | <b>Bus Connection</b> | IP Type          | IP Version |

| Θ                              |              |              |   | B     | B    | ÷        | 🗢ррс405_0       |             |                       | ppc405_virtex4   | 1.01.a     |

| Name 🔺                         |              | Version      |   |       |      | Ð        | ppc405_1        |             |                       | ppc405_virtex4   | 1.01.a     |

| 😟 Analog                       |              |              |   | 1     | 11   | - T .    | 🧇 plb           |             |                       | plb_v34          | 1.02.a     |

| <ul> <li>Arithmetic</li> </ul> |              |              |   |       |      | ÷.       | 🗢 opb           |             |                       | opb_v20          | 1.10.c     |

| 🖶 Bus                          |              |              |   |       |      |          | ⇒plb2opb        |             |                       | plb2opb_bridge   | 1.01.a     |

| 🛓 Bus Bridge                   |              |              |   | I T I |      |          | ⇒jtagppc_0      |             |                       | jtagppc_cntlr    | 2.00.a     |

| 🗄 Clock Cont                   | rol          |              |   |       | ``   | <u> </u> | LEDS            |             |                       | opb_gpio         | 3.01.Б     |

| 🛓 Communica                    | ation High-S | ipeed        |   | L T   |      |          | plb_bram_if_cn  | tlr_1       |                       | plb_bram_if_cntl |            |

| 🗄 Communica                    | ation Low-S  | peed         |   |       | - T. | <b>-</b> | ppc2fir_0       |             |                       | ppc2fir          | 1.00.a     |

| 🗄 Debug                        |              |              |   | 📥     |      | _        | SOPB            |             | opb                   |                  |            |

| 🖻 DMA                          |              |              |   | T     |      |          | reset_block     |             |                       | proc_sys_reset   |            |