# Sundance Multiprocessor Technology Limited **Product Specification**

| Unit / Module Description: | Dual -ADC PXI Express Hybrid Peripheral Module |

|----------------------------|------------------------------------------------|

| Unit / Module Number:      | SMT702                                         |

| Document Issue Number:     | 8                                              |

| Issue Date:                | 15/05/2007                                     |

| Original Author:           | PhSR                                           |

# Product Specification for SMT702

Sundance Multiprocessor Technology Ltd, Chiltern House, Waterside, Chesham, Bucks. HP5 1PS.

This document is the property of Sundance and may not be copied nor communicated to a third party without prior written permission. © Sundance Multiprocessor Technology Limited 2006

Certificate Number FM 55022

## **Revision History**

| Issue | Changes Made                                                                                                                                             | Date     | Initials |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|

| 1     | First Release                                                                                                                                            | 07/02/07 | PhSR     |

| 2     | Power consumptions detailed. Block diagrams updated.<br>Virtex changed for a bigger part. Decision made for the<br>clock chip. FPGA Block Diagram added. | 23/02/07 | PhSR     |

| 3     | Layout added and registers (ADC and Frequency<br>Synthesizer) added. Comport removed                                                                     | 22/03/07 | PhSR     |

| 4     | JTAG Connector placed on Layout – Front panel connectors are all SMA.                                                                                    | 28/03/07 | PhSR     |

| 5     | DDR2 interface speed added, changed to hybrid PXI module                                                                                                 | 15/04/07 | PhSR     |

| 6     | Options PXIe/PXI clarified                                                                                                                               | 19/04/07 | PhSR     |

| 7     | SHB Connector added for connection to SMT712 board.<br>Diagrams updated.                                                                                 | 15/05/07 | PhSR     |

| 8     | Layout updated                                                                                                                                           | 09/10/07 | PhSR     |

## **Table of Contents**

| 1 |     | Intr   | oductio              | n7                                                                   |

|---|-----|--------|----------------------|----------------------------------------------------------------------|

| 2 |     | Rela   | ated Doo             | cuments                                                              |

|   | 2.1 | R      | eferenceo            | l Documents7                                                         |

| 3 |     | Acro   | onyms, A             | Abbreviations and Definitions8                                       |

|   | 3.1 | А      | cronyms              | and Abbreviations8                                                   |

|   | 3.2 | D      | efinitions           |                                                                      |

| 4 |     | Fun    | ctional              | Description8                                                         |

|   | 4.1 | B      | lock Diag            | ram8                                                                 |

|   | 4.2 | B      | lock Diag            | ram (Option PXIe)9                                                   |

|   | 4.3 | B      | lock Diag            | ram (option 32-bit PXI)9                                             |

|   | 4.4 | M      | Iodule De            | escription10                                                         |

|   | 4   | 4.4.1  | ADCs                 |                                                                      |

|   | 2   | 4.4.2  | FPGA                 |                                                                      |

|   | 4   | 4.4.3  | Configu              | ration (CPLD+Flash)10                                                |

|   | 2   | 4.4.4  | DDR2 N               | Memory                                                               |

|   | 4   | 4.4.5  | Clock ci             | rcuitry11                                                            |

|   | 2   | 4.4.6  | PXI Exp              | press Bus12                                                          |

|   | 2   | 4.4.7  | SHB Co               | nnector                                                              |

|   | 2   | 4.4.8  | Power S              | Supply (PXI Express Chassis)                                         |

|   | 2   | 4.4.9  | Power c              | onsumption13                                                         |

|   | 2   | 4.4.10 | o Power d            | lissipation14                                                        |

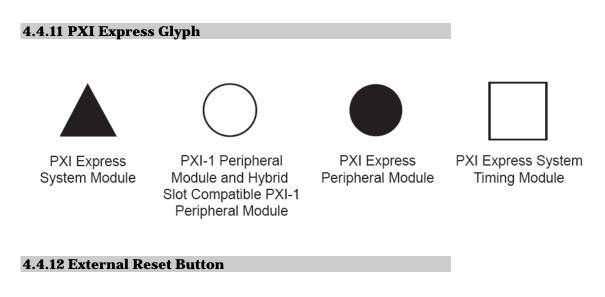

|   | 4   | 4.4.11 | PXI Exp              | press Glyph15                                                        |

|   | 4   | 4.4.12 | 2 Externa            | l Reset Button15                                                     |

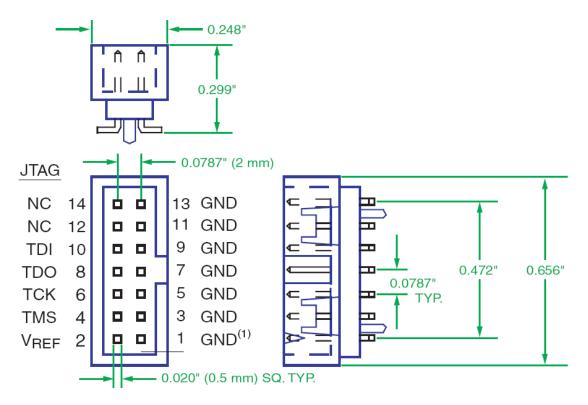

|   | 2   | 4.4.13 | 3 JTAG               |                                                                      |

|   | 2   | 4.4.14 | 4 PXI Exp            | press Hybrid Connectors 17                                           |

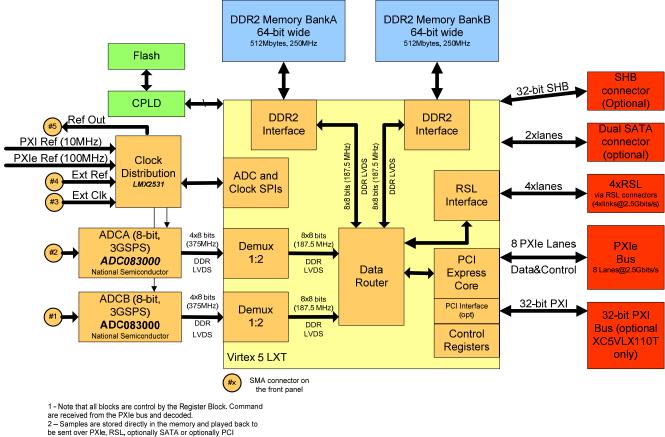

|   | 4.5 | F      | PGA Desi             | gn                                                                   |

|   | 2   | 4.5.1  | Control              | Registers                                                            |

|   |     | 4.5    | .1.1 M               | emory Map19                                                          |

|   |     | 4.5    | .1.2 Re              | egister Descriptions 20                                              |

|   | ]   | Reset  | Register             | - 0x0                                                                |

|   |     | 2      | 4.5.1.2.1            | ADCA (ADCo83000) Register 0x1 – Configuration Register 20            |

|   |     | 4      | 4.5.1.2.2            | ADCA (ADCo83000) Register 0x2 – Offset Adjust                        |

|   |     | 4      | 4.5.1.2.3            | ADCA (ADCo83000) Register 0x3 – Full Scale Voltage Adjust 21         |

|   |     | 2      | 4.5.1.2.4            | ADCA (ADCo83000) Register oxD – Extended Clock Phase Adjust Fine. 22 |

|   |     |        | 4.5.1.2.5<br>Coarse. | ADCA (ADCo83000) Register oxE – Extended Clock Phase Adjust 22       |

|    |       | 4.5.1.2.6             | ADCA (ADCo83000) Register oxF – Test Pattern register22<br>ADCB (ADCo83000) Register ox1 – Configuration Register23 |

|----|-------|-----------------------|---------------------------------------------------------------------------------------------------------------------|

|    |       | 4.5.1.2.7             |                                                                                                                     |

|    |       | 4.5.1.2.8             | ADCB (ADC083000) Register 0x2 – Offset Adjust23                                                                     |

|    |       | 4.5.1.2.9             | ADCB (ADC083000) Register 0x3 – Full Scale Voltage Adjust24                                                         |

|    |       | 4.5.1.2.10<br>Fine.   | ADCB (ADCo83000) Register oxD – Extended Clock Phase Adjust<br>24                                                   |

|    |       | 4.5.1.2.11<br>Coarse. | ADCB (ADCo83000) Register oxE – Extended Clock Phase Adjust 25                                                      |

|    |       | 4.5.1.2.12            | ADCB (ADCo83000) Register oxF – Test Pattern register25                                                             |

|    |       | 4.5.1.2.13            | Frequency Synthesizer (LMX2531) Register Ro25                                                                       |

|    |       | 4.5.1.2.14            | Frequency Synthesizer (LMX2531) Register R126                                                                       |

|    |       | 4.5.1.2.15            | Frequency Synthesizer (LMX2531) Register R226                                                                       |

|    |       | 4.5.1.2.16            | Frequency Synthesizer (LMX2531) Register R327                                                                       |

|    |       | 4.5.1.2.17            | Frequency Synthesizer (LMX2531) Register R4                                                                         |

|    |       | 4.5.1.2.18            | Frequency Synthesizer (LMX2531) Register R5 28                                                                      |

|    |       | 4.5.1.2.19            | Frequency Synthesizer (LMX2531) Register R629                                                                       |

|    |       | 4.5.1.2.20            | Frequency Synthesizer (LMX2531) Register R7 30                                                                      |

|    |       | 4.5.1.2.21            | Frequency Synthesizer (LMX2531) Register R8                                                                         |

|    |       | 4.5.1.2.22            | Frequency Synthesizer (LMX2531) Register R9                                                                         |

|    |       | 4.5.1.2.23            | Frequency Synthesizer (LMX2531) Register R1231                                                                      |

|    | 4.5.2 | e External            | Signal characteristics                                                                                              |

| 2  | 4.6 I | nterface D            | escription33                                                                                                        |

|    | 4.6.1 | Mechan                | ical Interface33                                                                                                    |

|    | 4.6.2 | e Electrica           | al Interface                                                                                                        |

| 5  | Ver   | rification            | Procedures                                                                                                          |

| 5  | 5.1 ( | CPLD and I            | FPGA detection                                                                                                      |

| 5  | 5.2 A | ADC conne             | ctions                                                                                                              |

| 5  | 5.3 A | ADC Distri            | bution                                                                                                              |

| 5  | 5.4 A | ADC Perfor            | mance                                                                                                               |

| 6  | Rev   | view Proc             | edures                                                                                                              |

| 7  | Val   | idation P             | rocedures                                                                                                           |

| 8  | Tin   | ning Diag             | rams                                                                                                                |

| 9  | Cir   | cuit Desc             | ription / Diagrams                                                                                                  |

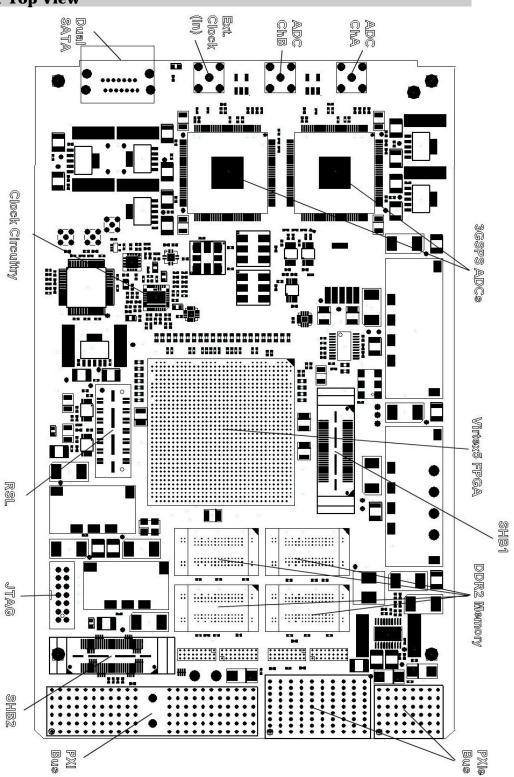

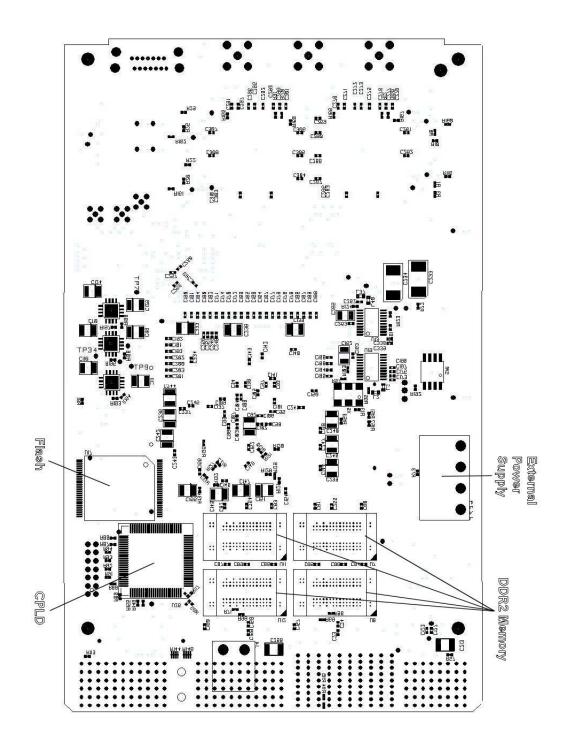

| 10 | Boa   | ard Layou             | ıt                                                                                                                  |

| 1  | 0.1 7 | Top View              |                                                                                                                     |

| 1  | 0.2 I | Bottom Vie            | w35                                                                                                                 |

| 11 | Pin   | out                   |                                                                                                                     |

| 12 | Suj   | oport Pac             | kages                                                                                                               |

| 13 | Physical Properties  | . 36 |

|----|----------------------|------|

| 14 | Safety               | . 36 |

| 15 | ЕМС                  | . 36 |

| 16 | Ordering Information | . 36 |

## **Table of Figures**

## **1** Introduction

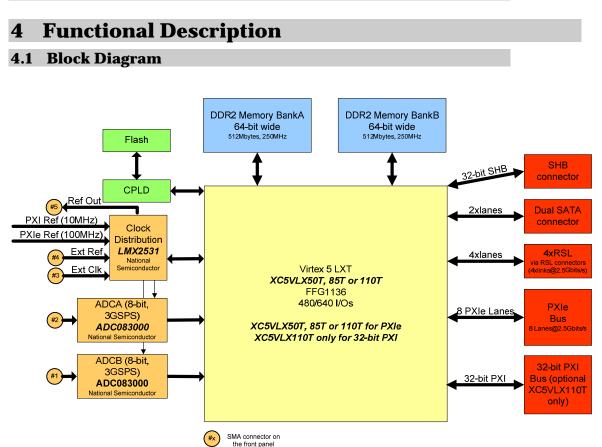

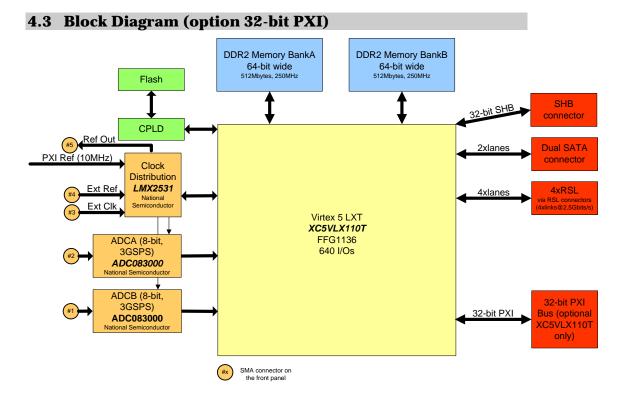

The SMT702 is a PXI Express (opt. Hybrid) Peripheral Module (3U), which integrates two fast 8-bit ADCs, a clock circuitry, 2 banks of DDR2 Memory and a Virtex5 Xilinx FPGA, under the 3U format.

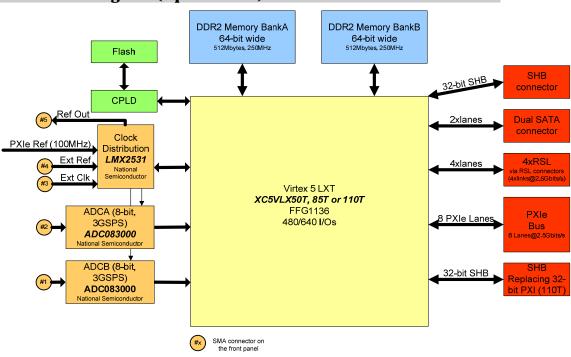

The PXIe specification integrates PCI Express signalling into the PXI standard for more backplane bandwidth. It also enhances PXI timing and synchronisation features by incorporating a 100MHz differential reference clock and triggers. The SMT702 can also integrate the standard 32-bit PXI signalling as an option.

Both ADC chips are identical and can produce 3 Giga-samples per second each, with an 8-bit resolution. The manufacturer is National Semiconductor and the part number is ADC083000. Analog-to-Digital converters are clocked by circuitry based on a PLL coupled with a VCO in order to generate a low-jitter signal. The ADC083000 is capable to achieve 7 bits of ENOB, 44dBs of SNR and 54dBs of SFDR. The full bandwidth is 3GHz. Each ADC integrates settings such as offset and scale factor, which makes the pair of ADC suitable to be combined together in order to make a 6GSPS single Analog to Digital converter. This will be subject to a specific application note.

An on-board PLL+VCO chip ensure a stable fixed sampling frequency (maximum rate), in order for the board to be used as digitiser without the need of external clock signal. The PLL will be able to lock the VCO either on the on-board 100MHz reference or the 100MHz PXI express reference (or 10MHz PXI reference depending on option) or on an external reference signal. The sampling clock for the converters can be either coming from the PLL+VCO chip or from an external source. The chip used is a National Semiconductor part: LMX2531LQ1500. The reference clock selected is also output on a connector in order to pass it to an other module.

The Virtex5 FPGA is responsible for controlling all interfaces, including PXI (32-bit) and PXIe (8 lanes allocated – depending on PXIe chassis, 4 or 8 lanes would be used), as well as routing samples. On the SMT702 the FPGA is an XC5VLX50T, which is footprint compatible with XC5VLX85T and XC5VLX110T. Note that all Virtex5s connect PXIe and only the XC5VLX110T will allow the full 32-bit PXI format

Two DDR2 memory banks are accessible by the FPGA in order to store data on the fly.

An SHB connector is available (XC5VLX110T only) in order to transfer data/samples to an other Sundance module.

All analog connectors on the front panel are SMA.

## 2 Related Documents

### 2.1 Referenced Documents

1 - National Semiconductor ADC083000:

http://www.national.com/pf/DC/ADCo83000.html

2 – National Semiconductor LMX2531LQ1500:

http://www.national.com/pf/LM/LMX2531LQ1500E.html

3 - Virtex5 FPGA:

http://www.xilinx.com/products/silicon\_solutions/fpgas/virtex/virtex5/index.htm

4 - PXIe specifications: <u>http://www.pxisa.org/Spec/PXIEXPRESS\_HW\_SPEC\_R1.PDF</u>

5 – Micron 2Gigabit DDR2 chip MT47H128M16:

http://download.micron.com/pdf/datasheets/dram/ddr2/2gbddr2.pdf

```

Product Specification SMT702

```

Page 7 of 36

## **3** Acronyms, Abbreviations and Definitions

### 3.1 Acronyms and Abbreviations

#### **PXIe** : PXI Express.

**SNR**: Signal-to-Noise Ratio. It is expressed in dBs. It is defined as the ratio of a signal power to the noise power corrupting the signal.

**SINAD**: Signal-to-Noise Ratio plus Distorsion. Same as SNR but includes harmonics too (no DC component).

**ENOB**: Effective Number Of Bits. This is an alternative way of defining the Signal-to-Noise Ratio and Distorsion Ratio (or SINAD). This means that the ADC is equivalent to a perfect ADC of ENOB number of bits.

**SFDR**: Spurious-Free Dynamic Range. It indicates in dB the ratio between the powers of the converted main signal and the greatest undesired spur.

### **3.2 Definitions**

Figure 1 - SMT702 Block Diagram.

### 4.2 Block Diagram (Option PXIe)

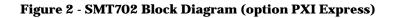

Figure 3 - SMT702 Block Diagram (32-bir PXI Option)

### 4.4 Module Description

### 4.4.1 ADCs

The ADCs are 8-bit parts from National Semiconductor (ADC083000). On the SMT702, each ADC can achieve up to 3 GSPS, in DDR mode.

Both ADCs are used in the extended mode. For more information, please refer to the ADCo83000 datasheet (National Semiconductor). This implies that they are configured using a Serial Interface implemented in the FPGA.

The typical Bit Error Rate (BER) of the ADCo83000 is 10<sup>-18</sup>. The maximum achievable SNR is 44dBs and the maximum SFDR achievable is 54dBs. These are the manufacturer figures.

#### 4.4.2 FPGA

The FPGA fitted as standard on the SMT702 is part of the Virtex5 LXT family: XC5VLX50T. The package used if FFG1136. It is footprint compatible with the XC5VLX85T and XC5VLX110T.

The FPGA should be at least a -2 speed grade, or -3 for an even faster FPGA.

The parts mentioned above are also footprint compatible with the SXT series: XC5VSX50T and XC5VSX95T. The SXT series implements a DSP48E core, which if used on the SMT702 may result power consumption problem such as exceeding the PXI Express Hybrid 3U Peripheral Module limits.

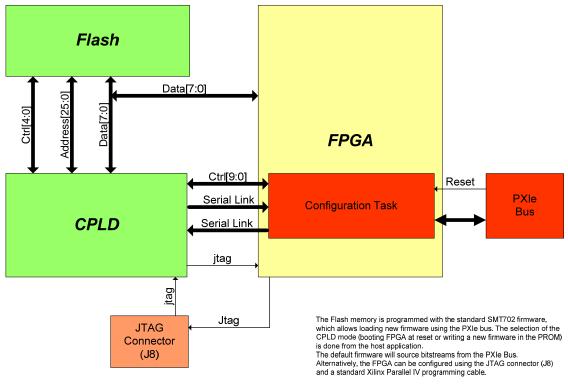

#### 4.4.3 Configuration (CPLD+Flash)

The FPGA gets its configuration at power up from the Flash memory via a CPLD.

Once the FPGA configured, the contents of the flash can be dynamically changed. Words are received from the PXI Express bus and passed to the CPLD that writes them in the Flash memory. A control word will be dedicated for reconfiguring the FPGA without the need of powering off and back on the board.

This allows the SMT702 to be used as a development platform for signal processing algorithms implementation.

The following diagram show how the connection are made on the board between the CPLD, the Flash memory and the FPGA:

Figure 4 - Configuration (Flash).

### 4.4.4 DDR2 Memory

Two banks of DDR2 memory are available on the SMT702, directly connected to the FPGA. Interfaces are part of the FPGA design. Each bank is 64-bit wide and 64-Meg deep, so each bank can store up to 512 Mega samples. Each memory bank is dedicated to one ADC.

Xilinx provides performances of a DDR2 interface as being: 200MHz for a -1 part, 267MHz for a -2 part and 333MHz for a -3 part.

Memory burst read or write operations, in order to achieve storage real-time of the ADC samples, should be done under a minimum clock of 187.5 MHz. Clocking the memory interface at 250MHz would allow achieving this figure.

#### 4.4.5 Clock circuitry

An on-board PLL+VCO chip ensure a stable fixed sampling frequency (maximum rate, i.e. 1500MHz), in order for the board to be used as digitiser without the need of external clock signal. The PLL will be able to lock the VCO either on the 10MHz PXI reference or the 100MHz PXI express reference or on an external reference signal. The sampling clock for the converters can be either coming from the PLL+VCO chip or from an external source. The chip used is a National Semiconductor part: LMX2531LQ1500.

The selection Internal/External clock is made via a bit in the control register. The same applies to the selection of the reference clock.

Note that the PLL+VCO chip also has the possibility to output half of the fixed VCO frequency, i.e. 1500/2=750MHz.

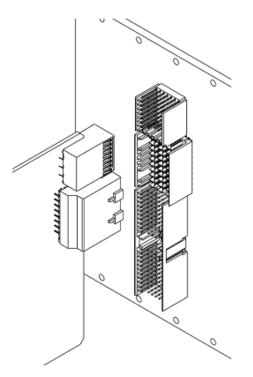

#### 4.4.6 PXI Express Bus

As standard, the SMT702 is a 3U PXI Express peripheral module, which means it comes with two PXI Express connectors: XP4 (PXI timing and synchronisation signals) and XP3 (x8 PCI Express and additional synchronisation signals). The SMT702 dedicates 8 lanes to the PXI Express bus, which gives an effective bandwidth per direction of 16Gb/s. It also implies core and user clocks to be 250 MHz. Note that not all PXIe Express chassis can handle 8 lanes on peripheral modules.

The standard SMT702 can plug in any PXI Express Peripheral Slot or any PXI Express Hybrid Slot.

Figure 5 - Standard SMT702 - PXI Express Peripheral Module

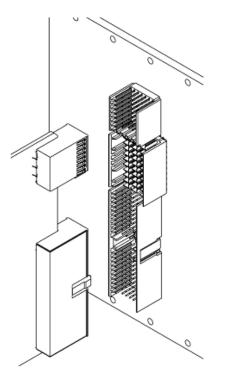

Optionally, the module can be a 3U Hybrid Peripheral Slot Compatible PXI-1 Module, means it comes with two connectors: XP4 (PXI timing and synchronisation signals) and P1 (32-bit, 33MHz PCI Signals). This version of SMT702 can only plug in any PXI Express Hybrid Slot

Figure 6 - SMT702 (opt.) - Hybrid Peripheral Slot Compatible PXI-1 Module

### 4.4.7 SHB Connector

An SHB Connector is available from the FPGA (only with XC5VLX110T). It maps 32 singleended data lines and a set of control signals including a clock.

It can be used to transfer samples to an other Sundance module, for instance the SMT712.

### 4.4.8 Power Supply (PXI Express Chassis)

The PXI Express specifications defines the maximum power consumption of 3U PXI Express peripheral modules as:

- 12-Volt rail: 2 Amps maximum (24 watts),

- 3.3-Volt rail: 3 Amps maximum (**10 watts**),

- 5-Volt rail (5Vaux): 1 Amp maximum.

An optional external power connector is available for external sources of the above rails. This should be carefully assessed as the fact of using an external power source may not meet the PXI Express specifications requirements.

#### 4.4.9 Power consumption

The FPGA and the DDR2 memory block will be powered from the 12-Volt PXI rail, whereas the ADCs and the clock circuitry will have their own supplies derived from the 3.3-Volt PXI rail.

### Virtex5 FPGA (Worst case XC5VLX110T)(19.0 watts)

The XC5VLX50T is the part that will be fitted by default. Footprint compatible parts include XC5LX85T and XC5VLX110T (XC5VSX50T and XC5VSX95T). The following power estimation has been done using a Xilinx spreadsheet, targeting the XC5VLX110T, with 98%

of its LUTs and Flip-Flips used, an 8-lane PCI Express core, 128 DDR lines and the rest of the IOs set to standard LVTTL.

Note that in the case of the XC5VSX95T, using all 640 DSP slices would add an extra 2.7 watts to Vccint.

Vccint = 1.0 Volt / Estimated current = 11Amps [11 watts]

Vccaux = 2.5 Volts / Estimated current = 825mA [2.0 watts]

Vcco\_18 = 1.8 Volts / Estimated current = 460mA [0.82 watt]

Vcco\_33 = 3.3 Volts / Estimated current = 639mA [2.11 watt]

Vccmgt = 1 Volt / Estimated current = 294mA [0.294 watt]

Vccmgpll = 1.2 Volts / Estimated power = 198mA [0.238 watt]

Vtttx = 1.2 Volts / Estimated power = 390mA [0.468 watt]

Vttrx = 1.2 Volts / Estimated power = 72mA [0.086 watt]

The above figures stand as the worst case, where an XC5VLX110T is fitted with a chip full working at 500MHz. This will not be the case of the standard firmware provided with the board. In case the FPGA design gets to be modified, it is strongly recommended that an power consumption analysis is performed in order to check that 19 watt of total power is not exceeded.

### <u>Memory DDR2 – 2 banks of 1Gbytes (5 watts)</u>

Vdd = Vddl = Vddq = 1.8V / Maximum current per chip = 355mA (8 chips – Micron MT47H128M16-37E - in total so 2.8 Amps). This does not include the termination resistors.

Vreference = Vddq/2 = 0.9V

Note that downsizing the memory capacity to 2 banks of 512Mbytes (MT47H64M16-37E) would reduce the current consumption per chip of 25mA (330mA) and would reduce power consumption down to 4.7 watts.

Note that downsizing the memory capacity to 2 banks of 256Mbytes (MT47H32M16-37E) would reduce the current consumption per chip of 15mA (340mA) and would reduce power consumption down to 4.9 watts.

### ADCs (5.6 Watts)

Va = Vdr = 1.9 Volts / Maximum current per ADC = 945mA

### <u>Clock chip</u>

Vccdig = Vccbuf = Vccvco = Vccvco = 3.0 Volts / maximum current = 46mA

#### 4.4.10 Power dissipation

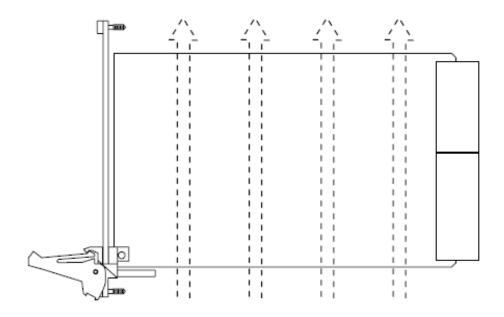

The PXI Express chassis receiving the SMT702 module should provide enough forced air flow in order to dissipate the heat generated by the module. The air flow must be going against gravity or upwards, as specified in the PXI Specification.

It is also specified that a 3U PXI Express module should not dissipate more than 30 Watts of heat.

The following picture shows the direction of the forced air flow across a 3U PXI Express module:

Figure 7 - Forced airflow for a 3U module.

A PXI Express rack has a capacity of dissipating 30 watts of heat per slot using forced aircooling system via typically two 110-cfm fans with filter.

Tbd.

### 4.4.13 JTAG

A connector (J8) is specifically dedicated for FPGA and CPLD detection and programming. Both the CPLD and the FPGA are part of the JTAG chain. A 14-position (2x7) connector (2mm) is available and shows TDI, TDO, TCK and TMS lines, as well as a Ground and a reference voltage, as shown below:

### Figure 8 - JTAG Connector.

It can connect directly to a Xilinx Parallel IV cable using the ribbon cable provided by Xilinx. The connector is a Molex part: Molex 87831-1428.

Figure 9 - Photo of a Xilinx Parallel IV cable and its ribbon cable for JTAG connection

### 4.4.14 PXI Express Hybrid Connectors

As being a PXI Express Hybrid Peripheral Module, the SMT702 is a 3U card with 2 PXI connectors, XP4 and XP3 or P1. The following table shows their pinouts.

| Pin   | Z            | Α            | В         | С             | D             | E         | F            |                                                                                                                                                              |  |

|-------|--------------|--------------|-----------|---------------|---------------|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | GND          | GA4          | GA3       | GA2           | GA1           | GA0       | GND          |                                                                                                                                                              |  |

| 2     | GND          | 5Vaux        | GND       | SYSEN#        | WAKE#         | ALERT#    | GND          |                                                                                                                                                              |  |

| 3     | GND          | 12V          | 12V       | GND           | GND           | GND       | GND          |                                                                                                                                                              |  |

| 4     | GND          | GND          | GND       | 3.3V          | 3.3V          | 3.3V      | GND          | XP4 / XJ4 Connector                                                                                                                                          |  |

| 5     | GND          | PXI TRIG3    | PXI TRIG4 | PXI TRIG5     | GND           | PXI TRIG6 | GND          |                                                                                                                                                              |  |

| 6     | GND          | PXI TRIG2    | GND       | ATNLED        | PXI STAR      | PXI CLK10 | GND          |                                                                                                                                                              |  |

| 7     | GND          | PXI TRIG1    | PXI TRIG0 | ATNSW#        | GND           | PXI TRIG7 | GND          |                                                                                                                                                              |  |

| 8     | GND          | RSV          | GND       | RSV           | PXI LBL6      | PXI LBR6  | GND          |                                                                                                                                                              |  |

| Pin   | А            | В            | ab        | С             | D             | cd        | E            | F ef 🗙                                                                                                                                                       |  |

| 1     | PXIe CLK100+ | PXIe CLK100- | GND       | PXIe SYNC100+ | PXIe SYNC100- | GND       | PXIe DSTARC+ | PXIe DSTARC GND                                                                                                                                              |  |

| 2     | PRSNT#       | PWREN#       | GND       | PXIe DSTARB+  | PXIe DSTARB-  | GND       | PXIe DSTARA+ | F el XP<br>PXIe DSTARC- GND<br>PXIe DSTARA- GND<br>RSV GND<br>1RefCIK- GND<br>40EErd SND                                                                     |  |

| 3     | SMBDAT       | SMBCLK       | GND       | RSV           | RSV           | GND       | RSV          | RSV GND                                                                                                                                                      |  |

| 4     | MPWRGD       | PERST#       | GND       | RSV           | RSV           | GND       | 1RefClk+     | 1RefClk- GND                                                                                                                                                 |  |

| 5     | 1PETp0       | 1PETn0       | GND       | 1PERp0        | 1PERn0        | GND       | 1PETp1       | 1PETn1 GND CO                                                                                                                                                |  |

| 6     | 1PETp2       | 1PETn2       | GND       | 1PERp2        | 1PERn2        | GND       | 1PERp1       | TPE INT     GND     O       1PERn1     GND     O       1PETn4     GND     O       1PERn4     GND     O       1PERn4     GND     O       1PERn7     GND     O |  |

| 7     | 1PETp3       | 1PETn3       | GND       | 1PERp3        | 1PERn3        | GND       | 1PETp4       | 1PETn4 GND                                                                                                                                                   |  |

| 8     | 1PETp5       | 1PETn5       | GND       | 1PERp5        | 1PERn5        | GND       | 1PERp4       | 1PERn4 GND                                                                                                                                                   |  |

| 9     | 1PETp6       | 1PETn6       | GND       | 1PERp6        | 1PERn6        | GND       | 1PETp7       | 1PETn7 GND 🛱                                                                                                                                                 |  |

| 10    | RSV          | RSV          | GND       | RSV           | RSV           | GND       | 1PERp7       | 1PERn7 GND 9                                                                                                                                                 |  |

| Pin   | Z            | A            | В         | С             | D             | E         | F            |                                                                                                                                                              |  |

|       | GND          | 5V           | REQ64#    | ENUM#         | 3.3V          | 5V        | GND          |                                                                                                                                                              |  |

|       | GND          | AD[1]        | 5V        | V(VO)         | AD[0]         | ACK64#    | GND          |                                                                                                                                                              |  |

| 23    | GND          | 3.3V         | AD[4]     | AD[3]         | 5V            | AD[2]     | GND          |                                                                                                                                                              |  |

| 22    | GND          | AD[7]        | GND       | 3.3V          | AD[6]         | AD[5]     | GND          |                                                                                                                                                              |  |

| 21    | GND          | 3.3V         | AD[9]     | AD[8]         | M66EN         | C/BE[0]#  | GND          |                                                                                                                                                              |  |

|       | GND          | AD[12]       | GND       | V(VO)         | AD[11]        | AD[10]    | GND          |                                                                                                                                                              |  |

| 19    | GND          | 3.3V         | AD[15]    | AD[14]        | GND           | AD[13]    | GND          |                                                                                                                                                              |  |

| 18    | GND          | SERR#        | GND       | 3.3V          | PAR           | C/BE[1]#  | GND          |                                                                                                                                                              |  |

| 17    | GND          | 3.3V         | IPMB_SCL  | IPMB_SDA      | GND           | PERR#     | GND          |                                                                                                                                                              |  |

| 16    | GND          | DEVSEL#      | <br>GND   | V(VO)         | STOP#         | LOCK#     | GND          |                                                                                                                                                              |  |

| 15    | GND          | 3.3V         | FRAME#    | IRDY#         | BD_SEL#       | TRDY#     | GND          | D4 / 14 Commont                                                                                                                                              |  |

| 12-14 |              |              |           | Key Area      | •             |           |              | P1 / J1 Connector                                                                                                                                            |  |

| 11    | GND          | AD[18]       | AD[17]    | AD[16]        | GND           | C/BE[2]#  | GND          |                                                                                                                                                              |  |

| 10    | GND          | AD[21]       | GND       | 3.3V          | AD[20]        | AD[19]    | GND          |                                                                                                                                                              |  |

| 9     | GND          | C/BE[3]#     | IDSEL     | AD[23]        | GND           | AD[22]    | GND          |                                                                                                                                                              |  |

| 8     | GND          | AD[26]       | GND       | V(VO)         | AD[25]        | AD[24]    | GND          |                                                                                                                                                              |  |

| 7     | GND          | AD[30]       | AD[29]    | AD[28]        | GND           | AD[27]    | GND          |                                                                                                                                                              |  |

| 6     | GND          | REQ#         | GND       | 3.3V          | CLK           | AD[31]    | GND          |                                                                                                                                                              |  |

| 5     | GND          | BRSVP1A5     | BRSVP1B5  | RST#          | GND           | GNT#      | GND          |                                                                                                                                                              |  |

| 4     | GND          | IPMB_PWR     | HEALTHY#  | V(VO)         | INTP          | INTS      | GND          |                                                                                                                                                              |  |

| 3     | GND          | INTA#        | INTB#     | INTC#         | 5V            | INTD#     | GND          |                                                                                                                                                              |  |

| 2     | GND          | тск          | 5V        | TMS           | TDO           | TDI       | GND          |                                                                                                                                                              |  |

| 1     | GND          | 5V           | -12V      | TRST#         | +12V          | 5V        | GND          |                                                                                                                                                              |  |

The SMT702 implements up to eight 2.5-Gigabit PCI Express lanes, allowing a maximum data transfer of 2 gigabytes per second. It also implements optionally a 32-bit, 33-MHz PCI interface.

### 4.5 FPGA Design

### Figure 10 - Block Diagram - FPGA Design (standard Firmware).

### 4.5.1 Control Registers

The Control Registers drive the complete functionality of the SMT702. They are setup via the PXIe bus (standard firmware provided). The settings of the ADCs, triggers, clocks and the configuration of the RSL/PXI interfaces (optional SATA) and the internal FPGA data path settings can be configured.

The data passed on to the SMT702 over the PXIe bus must conform to a certain packet structure. Only valid packets will be accepted and only after acceptance of a packet will the appropriate settings be implemented. Each packet will start with a command (2 bits – 0x1 for a write operation – 0x2 for a read operation) information, followed by a register address (6 bits – see table), followed by a 24-bit data. This structure is illustrated in the following figure:

|      | Byte Content |                                                                             |           |           |           |           |           |           |  |  |  |

|------|--------------|-----------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|--|

| Byte | Bit 7        | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0 |           |           |           |           |           |           |  |  |  |

| 3    | Command<br>1 | Command<br>O                                                                | Address 5 | Address 4 | Address 3 | Address 2 | Address 1 | Address o |  |  |  |

| 2    | Data 23      | Data 22                                                                     | Data 21   | Data 20   | Data 19   | Data 18   | Data 17   | Data 16   |  |  |  |

| 1    | Data 15      | Data 14                                                                     | Data 13   | Data 12   | Data 11   | Data 10   | Data 9    | Data 8    |  |  |  |

| 0    | Data 7       | Data 6                                                                      | Data 5    | Data 4    | Data 3    | Data 2    | Data 1    | Data o    |  |  |  |

**Figure 11 – Setup Packet Structure.**

### **4.5.1.1 Memory Map**

The write packets must contain the address where the data must be written to and the read packets must contain the address where the required data must be read. The following figure shows the memory map for the writable and readable Control Registers on the SMT702:

| Address | Writable Registers                          | Readable Registers                                                       |

|---------|---------------------------------------------|--------------------------------------------------------------------------|

| 0x00    | Reset Register.                             | Reserved.                                                                |

| 0x01    | Test Register.                              | Test Register.                                                           |

| 0x02    | Update and Read-back command Register       | Firmware Version and Status bits.                                        |

| 0x03    |                                             |                                                                          |

| 0x11    | ADCA (ADCo83000) Register 0x1.              | Read-back (FPGA Register) ADCA (ADC083000)<br>Register 0x1.              |

| 0x12    | ADCA (ADC083000) Register 0x2.              | Read-back (FPGA Register) ADCA (ADC083000)<br>Register 0x2.              |

| 0x13    | ADCA (ADC083000) Register 0x3.              | Read-back (FPGA Register) ADCA (ADC083000)<br>Register 0x3.              |

| 0x1D    | ADCA (ADC083000) Register oxD.              | Read-back (FPGA Register) ADCA (ADC083000)<br>Register oxD.              |

| 0x1E    | ADCA (ADC083000) Register oxE.              | Read-back (FPGA Register) ADCA (ADCo83000)<br>Register 0x2<br>E.         |

| 0x1F    | ADCA (ADCo83000) Register oxF.              | Read-back (FPGA Register) ADCA (ADCo83000)<br>Register oxF.              |

| 0x21    | ADCB (ADC083000) Register 0x1.              | Read-back (FPGA Register) ADCB (ADC083000)<br>Register 0x1.              |

| 0x22    | ADCB (ADC083000) Register 0x2.              | Read-back (FPGA Register) ADCB (ADC083000)<br>Register 0x2.              |

| 0x23    | ADCB (ADC083000) Register 0x3.              | Read-back (FPGA Register) ADCB (ADC083000)<br>Register 0x3.              |

| 0x2D    | ADCB (ADC083000) Register oxD.              | Read-back (FPGA Register) ADCB (ADC083000)<br>Register oxD.              |

| Ox2E    | ADCB (ADCo83000) Register oxE.              | Read-back (FPGA Register) ADCB (ADC083000)<br>Register 0x2<br>E.         |

| 0x2F    | ADCB (ADC083000) Register oxF.              | Read-back (FPGA Register) ADCB (ADC083000)<br>Register oxF.              |

| 0x30    | Frequency Synthesizer (LMX2531) register Ro | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register Ro |

| 0x31    | Frequency Synthesizer (LMX2531) register R1 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R1 |

| 0x32    | Frequency Synthesizer (LMX2531) register R2 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R2 |

| 0x33    | Frequency Synthesizer (LMX2531) register R3 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R3 |

| 0x34    | Frequency Synthesizer (LMX2531) register R4 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R4 |

| 0x35    | Frequency Synthesizer (LMX2531) register R5 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R5 |

| 0x36    | Frequency Synthesizer (LMX2531) register R6 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R6 |

| 0x37    | Frequency Synthesizer (LMX2531) register R7 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R7 |

| 0x38    | Frequency Synthesizer (LMX2531) register R8 | Read-back (FPGA register) Frequency Synthesizer                          |

|         |                                             | •                                                                        |

|      |                                              | (LMX2531) register R8                                                     |

|------|----------------------------------------------|---------------------------------------------------------------------------|

| 0x39 | Frequency Synthesizer (LMX2531) register R9  | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R9  |

| 0x3A | Frequency Synthesizer (LMX2531) register R12 | Read-back (FPGA register) Frequency Synthesizer<br>(LMX2531) register R12 |

Note that all ADC registers are write-only, which means that the contents of the ADC registers can't be read-back from the ADC itself but can from the FPGA.

## 4.5.1.2 Register Descriptions

### **Reset Register – 0x0.**

|         | Reset Register – 0x0                                                        |             |             |      |          |             |             |          |  |

|---------|-----------------------------------------------------------------------------|-------------|-------------|------|----------|-------------|-------------|----------|--|

| Byte    | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0 |             |             |      |          |             | Bit 0       |          |  |

| 0       | Reserved                                                                    | Reserved    | Reserved    | Rese | Reserved |             | Reserved    | Reserved |  |

| Default | <b>'</b> 0'                                                                 | <b>'</b> 0' | <b>'</b> 0' | í,   | 0'       | <b>'</b> 0' | <b>'</b> 0' | ʻ0'      |  |

|         |       | Reset Register – 0x0 |  |  |  |  |  |  |  |

|---------|-------|----------------------|--|--|--|--|--|--|--|

| Setting | Bit O | Description          |  |  |  |  |  |  |  |

| 0       | 0     | tbd                  |  |  |  |  |  |  |  |

| 1       | 1     | tbd                  |  |  |  |  |  |  |  |

| Setting | Bit 1 | Description          |  |  |  |  |  |  |  |

| 0       | 0     | tbd                  |  |  |  |  |  |  |  |

| 1       | 1     | tbd                  |  |  |  |  |  |  |  |

# 4.5.1.2.1 ADCA (ADC083000) Register 0x1 – Configuration Register.

|         |          | ADCA (ADC083000) Register 0x1 – Configuration Register |             |          |             |             |          |          |

|---------|----------|--------------------------------------------------------|-------------|----------|-------------|-------------|----------|----------|

| Byte    | Bit 7    | Bit 6                                                  | Bit 5       | Bit 4    | Bit 3       | Bit 2       | Bit 1    | Bit 0    |

| 1       | Reserved | DRE                                                    | RTD         | DCS      | DCP         | nDE         | OV       | OE       |

| Default | '1'      | <b>'</b> 0'                                            | <b>'</b> 0' | '1'      | <b>'</b> 0' | <b>'</b> 0' | '1'      | '1'      |

| 0       | Reserved | Reserved                                               | Reserved    | Reserved | Reserved    | Reserved    | Reserved | Reserved |

| Default | '1'      | '1'                                                    | '1'         | '1'      | '1'         | '1'         | '1'      | '1'      |

|         |        | ADCA (ADC083000) Register 0x1 – Configuration Register              |  |  |  |  |  |  |

|---------|--------|---------------------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 14 | Bit 14 Description (DRE – Differential Reset Enable)                |  |  |  |  |  |  |

| 0       | 0      | Single-ended Reset enabled.                                         |  |  |  |  |  |  |

| 1       | 1      | fferential Reset enabled.                                           |  |  |  |  |  |  |

| Setting | Bit 13 | Description (RTD – resistor Trim Disable)                           |  |  |  |  |  |  |

| 0       | 0      | Normal Operation.                                                   |  |  |  |  |  |  |

| 1       | 1      | Input termination resistor is not trimmed during calibration cycle. |  |  |  |  |  |  |

| Setting | Bit 12 | Description (DCS – Duty Cycle Stabilizer)                           |  |  |  |  |  |  |

| 0       | 0      | Stabilisation circuit disabled.                                     |  |  |  |  |  |  |

| 1       | 1      | Duty Cycle Stabilizer applied to the sampling clock.                |  |  |  |  |  |  |

| Setting | Bit 11 | Bit 11 Description (DCP – DDR Clock Phase – DDR Mode only)          |  |  |  |  |  |  |

Product Specification SMT702

| 0       | 0      | o° phase – ADC output clock time-aligned with data.        |  |  |  |

|---------|--------|------------------------------------------------------------|--|--|--|

| 1       | 1      | 90° phase – ADc output clock placed in the middle of data. |  |  |  |

| Setting | Bit 10 | Description (nDE – DDR Enable)                             |  |  |  |

| 0       | 0      | DDr Mode.                                                  |  |  |  |

| 1       | 1      | SRD Mode.                                                  |  |  |  |

| Setting | Bit 9  | Description (OV – LVDS Output Voltage amplitude)           |  |  |  |

| 0       | 0      | Reduced output amplitude – 510mV.                          |  |  |  |

| 1       | 1      | Standard output amplitude – 710mV.                         |  |  |  |

| Setting | Bit 8  | Description (OE –Output Edge)                              |  |  |  |

| 0       | 0      | 1:4 Demux Mode (DDR Mode must be Selected).                |  |  |  |

| 1       | 1      | 1:2 Demux Mode (DDR Mode must be selected).                |  |  |  |

## 4.5.1.2.2 ADCA (ADC083000) Register 0x2 – Offset Adjust.

|         | ADCA (ADC083000) Register 0x2 – Offset Adjust |              |            |            |          |          |            |            |

|---------|-----------------------------------------------|--------------|------------|------------|----------|----------|------------|------------|

| Byte    | Bit 7                                         | Bit 6        | Bit 5      | Bit 4      | Bit 3    | Bit 2    | Bit 1      | Bit O      |

| 1       |                                               | Offset Value |            |            |          |          |            |            |

| Default |                                               | "0000000"    |            |            |          |          |            |            |

| 0       | Reserved                                      | Reserved     | Reserved   | Reserved   | Reserved | Reserved | Reserved   | Reserved   |

| Default | '1'                                           | '1'          | <b>'1'</b> | <b>'1'</b> | '1'      | '1'      | <b>'1'</b> | <b>'1'</b> |

|         |          | ADCA (ADC083000) Register 0x2 – Offset Adjust              |  |  |  |  |  |  |  |

|---------|----------|------------------------------------------------------------|--|--|--|--|--|--|--|

| Setting | Bit 8-15 | Bit 8-15 Description (Offset Adjust)                       |  |  |  |  |  |  |  |

| 0       | 0        | bit value - 0.176mV per bit – 0x0 is 0mv and 0xFF is 45mV. |  |  |  |  |  |  |  |

| Setting | Bit 7    | Description (Offset sign)                                  |  |  |  |  |  |  |  |

| 0       | 0        | Positive offset.                                           |  |  |  |  |  |  |  |

| 1       | 1        | Negative offset.                                           |  |  |  |  |  |  |  |

## 4.5.1.2.3 ADCA (ADC083000) Register 0x3 – Full Scale Voltage Adjust.

|         | ADCA (ADC083000) Register 0x3 – Full Scale Voltage Adjust |              |          |          |          |          |          |          |

|---------|-----------------------------------------------------------|--------------|----------|----------|----------|----------|----------|----------|

| Byte    | Bit 7                                                     | Bit 6        | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

| 1       |                                                           | Adjust Value |          |          |          |          |          |          |

| Default |                                                           |              |          | "1000    | 0000"    |          |          |          |

| 0       | Adjust<br>Value                                           | Reserved     | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved |

| Default | <b>'</b> 0'                                               | '1'          | '1'      | '1'      | '1'      | '1'      | '1'      | '1'      |

|         | ADCA (ADC083000) Register 0x3 – Full Scale Voltage Adjust |                                                                                                                     |  |  |  |  |  |  |

|---------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 7-15                                                  | Description (Full Scale Voltage Adjust)                                                                             |  |  |  |  |  |  |

| 0       | 0                                                         | 9-bit value – 20% adjustment around the nominal 700mVpp differential value – 0x0 is 560mVp-p and 0x1FF is 840mVp-p. |  |  |  |  |  |  |

### 4.5.1.2.4 ADCA (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine.

|         | ADCA (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine |                     |          |          |          |          |          |          |

|---------|------------------------------------------------------------------|---------------------|----------|----------|----------|----------|----------|----------|

| Byte    | Bit 7                                                            | Bit 6               | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1    | Bit O    |

| 1       |                                                                  | Phase Adjust (Fine) |          |          |          |          |          |          |

| Default |                                                                  | "00000000"          |          |          |          |          |          |          |

| 0       | Phase<br>Adjust                                                  | Reserved            | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved |

| Default | <b>'</b> 0'                                                      | '1'                 | '1'      | '1'      | '1'      | '1'      | '1'      | '1'      |

|         | AI       | ADCA (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine |  |  |  |  |  |

|---------|----------|------------------------------------------------------------------|--|--|--|--|--|

| Setting | Bit 7-15 | Description (Fine Adjust Magnitude)                              |  |  |  |  |  |

| 0       | 0        | oit value – With all bits set, adjust=110ps.                     |  |  |  |  |  |

### 4.5.1.2.5 ADCA (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse.

|         |             | ADCA (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse |            |              |          |          |          |          |

|---------|-------------|--------------------------------------------------------------------|------------|--------------|----------|----------|----------|----------|

| Byte    | Bit 7       | Bit 6                                                              | Bit 5      | Bit 4        | Bit 3    | Bit 2    | Bit 1    | Bit O    |

| 1       | ENA         |                                                                    | Phase Adju | ıst (Coarse) |          | LFS      | Reserved | Reserved |

| Default | <b>'</b> 0' |                                                                    |            |              |          | ʻ0'      | '1'      | '1'      |

| 0       | Reserved    | Reserved                                                           | Reserved   | Reserved     | Reserved | Reserved | Reserved | Reserved |

| Default | '1'         | '1'                                                                | '1'        | '1'          | '1'      | '1'      | '1'      | '1'      |

|         | AD        | ADCA (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse |  |  |  |  |  |  |

|---------|-----------|--------------------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 10    | escription (LFS – Low Frequency Sample Clock)                      |  |  |  |  |  |  |

| 0       | 0         | Sample Clock above 900MHz.                                         |  |  |  |  |  |  |

| 1       | 1         | ample Clock below 900MHz.                                          |  |  |  |  |  |  |

| Setting | Bit 11-14 | Description (Coarse Adjust Magnitude)                              |  |  |  |  |  |  |

| 0       | 0         | 4-bit value – Each LSB adds approximately 70ps of Clock Adjust.    |  |  |  |  |  |  |

| Setting | Bit 15    | Description (ENA - enable)                                         |  |  |  |  |  |  |

| 0       | 0         | Disabled.                                                          |  |  |  |  |  |  |

| 1       | 1         | Enabled.                                                           |  |  |  |  |  |  |

## 4.5.1.2.6 ADCA (ADC083000) Register 0xF – Test Pattern register.

|         | ADCA (ADC083000) Register 0xF – Test Pattern Register |                                                                             |          |          |             |          |          |          |  |  |

|---------|-------------------------------------------------------|-----------------------------------------------------------------------------|----------|----------|-------------|----------|----------|----------|--|--|

| Byte    | Bit 7                                                 | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0 |          |          |             |          |          |          |  |  |

| 1       | Reserved                                              | Reserved                                                                    | Reserved | Reserved | TPO         | Reserved | Reserved | Reserved |  |  |

| Default | '1'                                                   | '1'                                                                         | '1'      | '1'      | <b>'</b> 0' | '1'      | '1'      | '1'      |  |  |

| 0       | Reserved                                              | Reserved                                                                    | Reserved | Reserved | Reserved    | Reserved | Reserved | Reserved |  |  |

| Default | '1'                                                   | '1'                                                                         | '1'      | '1'      | '1'         | '1'      | '1'      | '1'      |  |  |

|         |        | ADCA (ADC083000) Register 0xF – Test Pattern Register |  |  |  |  |  |  |

|---------|--------|-------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 11 | Bit 11 Description (TPO – Test Pattern Output Enable) |  |  |  |  |  |  |

| 0       | 0      | Normal mode of Operation.                             |  |  |  |  |  |  |

| 1       | 1      | All ADC outputs in Test Pattern mode.                 |  |  |  |  |  |  |

# 4.5.1.2.7 ADCB (ADC083000) Register 0x1 – Configuration Register.

|         | ADCB (ADC083000) Register 0x1 – Configuration Register |                                          |          |          |             |             |          |          |  |  |

|---------|--------------------------------------------------------|------------------------------------------|----------|----------|-------------|-------------|----------|----------|--|--|

| Byte    | Bit 7                                                  | Bit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0 |          |          |             |             |          |          |  |  |

| 1       | Reserved                                               | DRE                                      | RTD      | DCS      | DCP         | nDE         | OV       | OE       |  |  |

| Default | '1'                                                    | <b>'</b> 0'                              | ʻ0'      | '1'      | <b>'</b> 0' | <b>'</b> 0' | '1'      | '1'      |  |  |

| 0       | Reserved                                               | Reserved                                 | Reserved | Reserved | Reserved    | Reserved    | Reserved | Reserved |  |  |

| Default | '1'                                                    | '1'                                      | '1'      | '1'      | '1'         | '1'         | '1'      | '1'      |  |  |

|         |        | ADCB (ADC083000) Register 0x1 – Configuration Register              |

|---------|--------|---------------------------------------------------------------------|

| Setting | Bit 14 | Description (DRE – Differential Reset Enable)                       |

| 0       | 0      | Single-ended Reset enabled.                                         |

| 1       | 1      | Differential Reset enabled.                                         |

| Setting | Bit 13 | Description (RTD – resistor Trim Disable)                           |

| 0       | 0      | Normal Operation.                                                   |

| 1       | 1      | Input termination resistor is not trimmed during calibration cycle. |

| Setting | Bit 12 | Description (DCS – Duty Cycle Stabilizer)                           |

| 0       | 0      | Stabilisation circuit disabled.                                     |

| 1       | 1      | Duty Cycle Stabilizer applied to the sampling clock.                |

| Setting | Bit 11 | Description (DCP – DDR Clock Phase – DDR Mode only)                 |

| 0       | 0      | o° phase – ADC output clock time-aligned with data.                 |

| 1       | 1      | 90° phase – ADc output clock placed in the middle of data.          |

| Setting | Bit 10 | Description (nDE – DDR Enable)                                      |

| 0       | 0      | DDr Mode.                                                           |

| 1       | 1      | SRD Mode.                                                           |

| Setting | Bit 9  | Description (OV – LVDS Output Voltage amplitude)                    |

| 0       | 0      | Reduced output amplitude – 510mV.                                   |

| 1       | 1      | Standard output amplitude – 710mV.                                  |

| Setting | Bit 8  | Description (OE –Output Edge)                                       |

| 0       | 0      | 1:4 Demux Mode (DDR Mode must be Selected).                         |

| 1       | 1      | 1:2 Demux Mode (DDR Mode must be selected).                         |

## 4.5.1.2.8 ADCB (ADC083000) Register 0x2 – Offset Adjust.

|         | ADCB (ADC083000) Register 0x2 – Offset Adjust |                                                                             |  |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Byte    | Bit 7                                         | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0 |  |  |  |  |  |  |  |  |  |

| 1       |                                               | Offset Value                                                                |  |  |  |  |  |  |  |  |  |

| Default |                                               | "0000000"                                                                   |  |  |  |  |  |  |  |  |  |

| 0       | Reserved |

|---------|----------|----------|----------|----------|----------|----------|----------|----------|

| Default | '1'      | '1'      | '1'      | '1'      | '1'      | '1'      | '1'      | '1'      |

|         |          | ADCB (ADC083000) Register 0x2 – Offset Adjust                |  |  |  |  |  |  |

|---------|----------|--------------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 8-15 | t 8-15 Description (Offset Adjust)                           |  |  |  |  |  |  |

| 0       | 0        | 8-bit value - 0.176mV per bit – 0x0 is omv and 0xFF is 45mV. |  |  |  |  |  |  |

| Setting | Bit 7    | t 7 Description (Offset sign)                                |  |  |  |  |  |  |

| 0       | 0        | Positive offset.                                             |  |  |  |  |  |  |

| 4       |          | Negative offset.                                             |  |  |  |  |  |  |

## 4.5.1.2.9 ADCB (ADC083000) Register 0x3 – Full Scale Voltage Adjust.

|         | ADCB (ADC083000) Register 0x3 – Full Scale Voltage Adjust |                                                                             |     |       |       |     |     |     |  |  |

|---------|-----------------------------------------------------------|-----------------------------------------------------------------------------|-----|-------|-------|-----|-----|-----|--|--|

| Byte    | Bit 7                                                     | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0 |     |       |       |     |     |     |  |  |

| 1       |                                                           | Adjust Value                                                                |     |       |       |     |     |     |  |  |

| Default |                                                           |                                                                             |     | "1000 | 0000" |     |     |     |  |  |

| 0       | Adjust<br>Value                                           |                                                                             |     |       |       |     |     |     |  |  |

| Default | <b>'</b> 0'                                               | '1'                                                                         | '1' | '1'   | '1'   | '1' | '1' | '1' |  |  |

|         |          | ADCB (ADC083000) Register 0x3 – Full Scale Voltage Adjust                                                           |  |  |  |  |  |  |

|---------|----------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 7-15 | Description (Full Scale Voltage Adjust)                                                                             |  |  |  |  |  |  |

| 0       | 0        | 9-bit value – 20% adjustment around the nominal 700mVpp differential value – 0x0 is 560mVp-p and 0x1FF is 840mVp-p. |  |  |  |  |  |  |

### 4.5.1.2.10 ADCB (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine.

|         |                 | ADCB (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine |     |       |       |     |     |     |  |  |

|---------|-----------------|------------------------------------------------------------------|-----|-------|-------|-----|-----|-----|--|--|

| Byte    | Bit 7           | Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                  |     |       |       |     |     |     |  |  |

| 1       |                 | Phase Adjust (Fine)                                              |     |       |       |     |     |     |  |  |

| Default |                 |                                                                  |     | "0000 | 0000" |     |     |     |  |  |

| 0       | Phase<br>Adjust |                                                                  |     |       |       |     |     |     |  |  |

| Default | ʻ0'             | '1'                                                              | '1' | '1'   | '1'   | '1' | '1' | '1' |  |  |

|         | AI       | ADCB (ADC083000) Register 0xD – Extended Clock Phase Adjust Fine |  |  |  |  |  |  |

|---------|----------|------------------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 7-15 | bit 7-15 Description (Fine Adjust Magnitude)                     |  |  |  |  |  |  |

| 0       | 0        | 9-bit value – With all bits set, adjust=110ps.                   |  |  |  |  |  |  |

### 4.5.1.2.11 ADCB (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse.

|         |             | ADCB (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse          |            |              |          |             |          |          |  |  |

|---------|-------------|-----------------------------------------------------------------------------|------------|--------------|----------|-------------|----------|----------|--|--|

| Byte    | Bit 7       | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0 |            |              |          |             |          |          |  |  |

| 1       | ENA         |                                                                             | Phase Adju | ıst (Coarse) |          | LFS         | Reserved | Reserved |  |  |

| Default | <b>'</b> 0' |                                                                             |            |              |          | <b>'</b> 0' | '1'      | '1'      |  |  |

| 0       | Reserved    | Reserved                                                                    | Reserved   | Reserved     | Reserved | Reserved    | Reserved |          |  |  |

| Default | '1'         | '1'                                                                         | '1'        | '1'          | '1'      | '1'         | '1'      | '1'      |  |  |

|         | AD        | ADCB (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse |  |  |  |  |  |  |

|---------|-----------|--------------------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 10    | Description (LFS – Low Frequency Sample Clock)                     |  |  |  |  |  |  |

| 0       | 0         | Sample Clock above 900MHz.                                         |  |  |  |  |  |  |

| 1       | 1         | Sample Clock below 900MHz.                                         |  |  |  |  |  |  |

| Setting | Bit 11-14 | Description (Coarse Adjust Magnitude)                              |  |  |  |  |  |  |

| 0       | 0         | 4-bit value – Each LSB adds approximately 70ps of Clock Adjust.    |  |  |  |  |  |  |

| Setting | Bit 15    | Description (ENA - enable)                                         |  |  |  |  |  |  |

| 0       | 0         | Disabled.                                                          |  |  |  |  |  |  |

| 1       | 1         | Enabled.                                                           |  |  |  |  |  |  |

## 4.5.1.2.12 ADCB (ADC083000) Register 0xF – Test Pattern register.

|         | ADCB (ADC083000) Register 0xF – Test Pattern Register |          |          |          |             |          |          |          |  |  |

|---------|-------------------------------------------------------|----------|----------|----------|-------------|----------|----------|----------|--|--|

| Byte    | Bit 7                                                 | Bit 6    | Bit 5    | Bit 4    | Bit 3       | Bit 2    | Bit 1    | Bit O    |  |  |

| 1       | Reserved                                              | Reserved | Reserved | Reserved | TPO         | Reserved | Reserved | Reserved |  |  |

| Default | '1'                                                   | '1'      | '1'      | '1'      | <b>'</b> 0' | '1'      | '1'      | '1'      |  |  |

| 0       | Reserved                                              | Reserved | Reserved | Reserved | Reserved    | Reserved | Reserved | Reserved |  |  |

| Default | '1'                                                   | '1'      | '1'      | '1'      | '1'         | '1'      | '1'      | '1'      |  |  |

|         |        | ADCB (ADC083000) Register 0xF – Test Pattern Register |  |  |  |  |  |  |

|---------|--------|-------------------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 11 | Bit 11 Description (TPO – Test Pattern Output Enable) |  |  |  |  |  |  |

| 0       | 0      | Normal mode of Operation.                             |  |  |  |  |  |  |

| 1       | 1      | All ADC outputs in Test Pattern mode.                 |  |  |  |  |  |  |

### 4.5.1.2.13 Frequency Synthesizer (LMX2531) Register R0.

|         | Frequency Synthesizer (LMX2531) Register R0                                 |        |    |               |           |             |     |  |  |  |  |

|---------|-----------------------------------------------------------------------------|--------|----|---------------|-----------|-------------|-----|--|--|--|--|

| Byte    | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0 |        |    |               |           |             |     |  |  |  |  |

| 2       |                                                                             | Reserv | ed |               | N[7:4]    |             |     |  |  |  |  |

| Default |                                                                             | '0000  | )' |               | '0000'    |             |     |  |  |  |  |

| 1       |                                                                             | N[3:0  | ]  |               | NUM[11:8] |             |     |  |  |  |  |

| Default |                                                                             | '0000  | )' |               |           | <b>'</b> 00 | 00' |  |  |  |  |

| 0       | NUM[7:0]                                                                    |        |    |               |           |             |     |  |  |  |  |

| Default |                                                                             |        |    | <u>'00000</u> | 0000'     |             |     |  |  |  |  |

Product Specification SMT702

|         |           | Frequency Synthesizer (LMX2531) Register R0   |  |  |  |  |  |  |

|---------|-----------|-----------------------------------------------|--|--|--|--|--|--|

| Setting | Bit 11-0  | Bit 11-0 Fractional numerator (NUM[11:0])     |  |  |  |  |  |  |

| 0       | 0         | Value between 0 (all 0s) and 4194303 (all 1s) |  |  |  |  |  |  |

| Setting | Bit 21-12 | N Counter (N[7:0])                            |  |  |  |  |  |  |

| 0       | 0         | Value between 0 (0x0) and 2039 (0x3F7)        |  |  |  |  |  |  |

## 4.5.1.2.14 Frequency Synthesizer (LMX2531) Register R1.

|         | Frequency Synthesizer (LMX2531) Register R1 |          |       |                |               |       |       |       |  |  |  |

|---------|---------------------------------------------|----------|-------|----------------|---------------|-------|-------|-------|--|--|--|

| Byte    | Bit 7                                       | Bit 6    | Bit 5 | Bit 4          | Bit 3         | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| 2       | Reserved Reserved                           |          |       |                |               |       |       |       |  |  |  |

| Default | `000000' '1' '0'                            |          |       |                |               |       |       |       |  |  |  |

| 1       |                                             | ICP[3:0] |       |                | N[10:8] NUM[2 |       |       |       |  |  |  |

| Default | 'ooo'                                       |          |       |                | '000'         |       | "(    | 00'   |  |  |  |

| 0       | NUM[19:12]                                  |          |       |                |               |       |       |       |  |  |  |

| Default |                                             |          |       | <b>'</b> 00000 | 000'          |       |       |       |  |  |  |

|         |           | Frequency Synthesizer (LMX2531) Register R1                                       |  |  |  |  |  |  |  |