## HARDWARE SPECIFICATION FOR

# RSL

(Rocket-IO Serial Link)

#### **Copyright © Sundance**

All rights reserved. No part of this document may be reproduced, translated, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission of the owner.

Note:

If this copy is no longer in use, return to sender.

| Document No.      | Revision | Date     | Page 1 of 24  |

|-------------------|----------|----------|---------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 1 01 24 |

## APPROVAL PAGE

| Name | Signature | Date |

|------|-----------|------|

|      |           |      |

|      |           |      |

|      |           |      |

|      |           |      |

## AUTHOR/S

| Name | Signature | Date |

|------|-----------|------|

|      |           |      |

|      |           |      |

| Document No.      | Revision | Date     | Page 2 of 24  |

|-------------------|----------|----------|---------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 2 01 24 |

## **DOCUMENT HISTORY**

| Date       | Initials | Revision | Description of change                                        |  |

|------------|----------|----------|--------------------------------------------------------------|--|

| 27/05/2005 | SM       | 1.0      | First Release – New document                                 |  |

| 19/05/2005 | SM       | 1.1      | Added: Sections 6, 7 and 8                                   |  |

| 13/09/2005 | JV       | 1.2      | Sections 6.1.3.1 updated lane mapping on connector           |  |

| 02/12/2005 | JV       | 1.3      | Added comment on input clock interaction for firmware design |  |

| 21/06/2006 | SM       | 1.4      | Added RSL test speed (section 4.1.5 Performances)            |  |

| 08/09/2006 | SM       | 1.5      | Corrected: section 4.1 RSL data rate                         |  |

| Document No.      | Revision | Date     | Page 3 of 24  |

|-------------------|----------|----------|---------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 5 61 24 |

## **TABLE OF CONTENTS**

| 1. | SCO                    | РЕ                                               | •••••                     |          | 7            |

|----|------------------------|--------------------------------------------------|---------------------------|----------|--------------|

|    | 1.1.                   | INTRODUCTION                                     |                           |          | 7            |

|    |                        | PURPOSE                                          |                           |          |              |

|    | 1.3.                   | APPLICABILITY                                    |                           |          |              |

| 2. | A DDI                  | LICABLE DOCUMENTS AND REI                        | FEDENCES                  |          | Q            |

|    |                        |                                                  |                           |          |              |

|    | 2.1.                   | APPLICABLE DOCUMENTS                             |                           |          |              |

|    | 2.1.1.                 |                                                  |                           |          |              |

|    | 2.1.2.<br>2.1.3.       |                                                  |                           |          |              |

|    | 2.1.3.<br>2.2.         | REFERENCES                                       |                           |          |              |

|    | 2.2.                   |                                                  |                           |          |              |

|    | 2.2.1.                 |                                                  |                           |          |              |

|    | 2.2.3.                 |                                                  |                           |          |              |

|    | 2.3.                   | PRECEDENCE                                       |                           |          |              |

| 3. | ACR                    | ONYMS, ABBREVIATIONS AND                         | DEFINITIONS               |          |              |

|    |                        | ACRONYMS AND ABBREVIATIONS                       |                           |          |              |

|    | 3.1.<br>3.2.           | DEFINITIONS                                      |                           |          |              |

|    |                        |                                                  |                           |          |              |

| 4. | REQ                    | UIREMENTS                                        | ••••••••••••••••••••••••• |          |              |

|    | 4.1.                   | PRIME ITEM DEFINITION                            |                           |          |              |

|    | 4.1.1.                 | 8                                                |                           |          |              |

|    | 4.1.2.                 | ···· j····                                       |                           |          |              |

|    | 4.1.3.                 | <b>J I I I I I I I I I I</b>                     |                           |          |              |

|    | 4.1.4.<br>4.1.5.       |                                                  |                           |          |              |

|    | 4.1.3.                 | SUNDANCE RSL MODELS                              |                           |          |              |

|    | 4.2.1.                 |                                                  |                           |          |              |

|    | 4.2.2.                 |                                                  |                           |          |              |

|    | 4.2.3.                 |                                                  |                           |          |              |

|    | 4.2.4.                 |                                                  |                           |          |              |

|    | 4.2.5.                 | 5                                                |                           |          |              |

|    |                        | MECHANICAL SPECIFICATIONS                        |                           |          |              |

|    | 4.3.1.                 |                                                  |                           |          |              |

|    | 4.3.2.                 |                                                  |                           |          |              |

|    | 4.3.3.<br>4.3.4.       | 0                                                |                           |          |              |

|    | 4.3.4.<br>4.3.5.       | Cables<br>Connector type/location                |                           |          |              |

|    | 4.3.3.                 | RsL PINOUTS                                      |                           |          |              |

|    | 4.4.1.                 | Naming convention                                |                           |          |              |

|    | 4.4.2.                 | 0                                                |                           |          |              |

|    | 4.4.3.                 |                                                  |                           |          |              |

|    | 4.4.4.                 | Rigid PCB and RSL Cable                          |                           |          |              |

|    | 4.5.                   | XILINX MULTI-GIGABYTES TRANSCEIV                 |                           |          |              |

|    | 4.5.1.                 | FPGA devices supported                           |                           |          |              |

|    | 4.5.2.                 | Rocket-IO Features                               |                           |          |              |

|    | <i>4.5.3</i> .<br>4.6. | <i>The Xilinx MGT Core</i><br>HARDWARE INTERFACE |                           |          |              |

|    | 4.0.<br><i>4.6.1</i> . |                                                  |                           |          |              |

|    | 4.6.2.                 |                                                  |                           |          |              |

|    | 4.6.3.                 | 5                                                |                           |          |              |

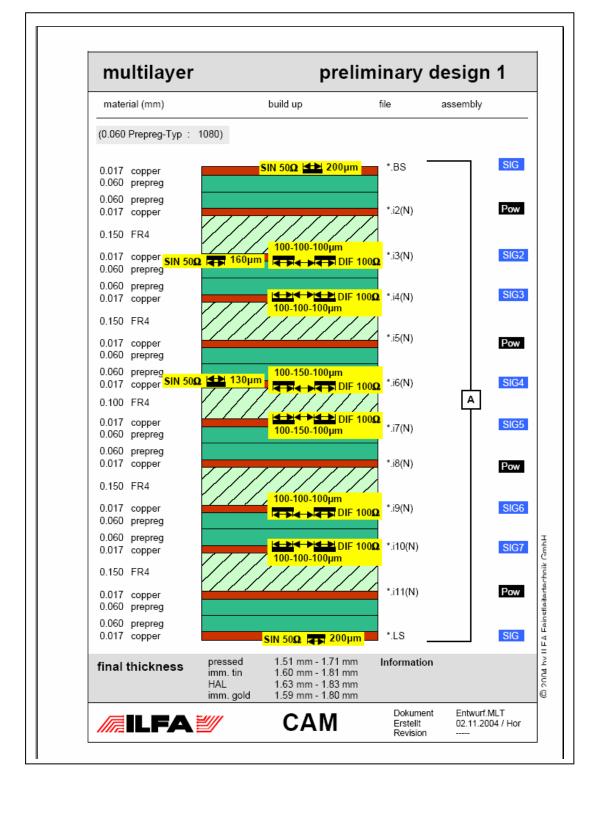

|    |                        | HARDWARE SPECIFICS                               |                           |          |              |

|    | 4.7.1.                 | RSL Printed Circuit Board                        |                           |          |              |

|    | 4.7.2.                 |                                                  |                           |          |              |

|    | 4.7.3.                 | J 0 1                                            |                           |          |              |

|    | 4.7.4.                 | 1 0                                              |                           |          |              |

|    | 4.7.5.                 | Speed grade and clock speed                      |                           |          |              |

|    |                        | Document No.                                     | Revision                  | Date     | D 4 604      |

|    | л                      | 000002H-spec.doc                                 | 1.5                       | 08/09/06 | Page 4 of 24 |

|    | ע                      | 00000211-spec.uut                                | 1.5                       | 00/07/00 |              |

| 5.  | QUA                    | LIFICATION REQUIREMENTS                     |                                         |          | 68           |

|-----|------------------------|---------------------------------------------|-----------------------------------------|----------|--------------|

| 4   | 5.1.                   | QUALIFICATION TESTS OF THE FIRMWAR          |                                         |          |              |

|     | 5.1.1.                 | RSL link test                               |                                         |          |              |

|     | 5.1.2.                 | 5                                           |                                         |          |              |

| -   | 5.2.                   | ERROR DETECTION                             |                                         |          |              |

| 6.  | РСВ                    | DESIGN: REVIEW CHECK LIST                   | ••••••••••••••••••••••••••••••••••••••• |          |              |

| 6   | 5.1.                   | SCHEMATICS                                  |                                         |          |              |

|     | 6.1.1.                 | 8 2                                         |                                         |          |              |

|     | 6.1.2.<br>6.1.3.       |                                             |                                         |          |              |

| f   | 6.2.                   | PCB LAYOUT                                  |                                         |          |              |

|     | 6.2.1.                 |                                             |                                         |          |              |

|     | 6.2.2.                 |                                             |                                         |          |              |

|     | 6.2.3.                 |                                             |                                         |          |              |

|     | 6.2.4.<br>6.2.5.       |                                             |                                         |          |              |

| f   | 0.2.3.<br>5.3.         | Design verification                         |                                         |          |              |

| ,   | 6.3.1.                 |                                             |                                         |          |              |

| 7.  | DESI                   | GN CHECKLIST                                |                                         |          | 88           |

|     | <b>DES</b><br>7.1.     | SCHEMATICS                                  |                                         |          |              |

|     | /.1.<br><i>7.1.1</i> . |                                             |                                         |          |              |

|     | 7.1.2.                 |                                             |                                         |          |              |

|     | 7.1.3.                 | Connectors                                  |                                         |          |              |

| 7   | 7.2.                   | PCB LAYOUT                                  |                                         |          |              |

|     | 7.2.1.<br>7.2.2.       |                                             |                                         |          |              |

|     | 7.2.2.                 |                                             |                                         |          | 90<br>89     |

|     | 7.2.4.                 | · · ·                                       |                                         |          |              |

|     | 7.2.5.                 | Differential pairs                          |                                         |          |              |

| 7   | 7.3.                   | DESIGN VERIFICATION                         |                                         |          |              |

|     | 7.3.1.                 |                                             |                                         |          |              |

|     | 7.3.2.<br>7.3.3.       | 5                                           |                                         |          |              |

| 8.  |                        | PLATE FOR BOARD REPORT                      |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     | 8.1.                   | CLOCK TERMINATIONS                          |                                         |          |              |

|     | 8.2.<br>8.3.           | OSCILLATORS AND PINOUT<br>CONNECTOR MAPPING |                                         |          |              |

|     | 3. <i>3</i> .<br>8.4.  | POLARITY INVERSION                          |                                         |          |              |

|     | 8.5.                   | CLOCK TRACKS LENGTH                         |                                         |          |              |

|     | 8.6.                   | DIFFERENTIAL PAIRS TRACK LENGTH CC          | NNECTION AND VIAS                       |          |              |

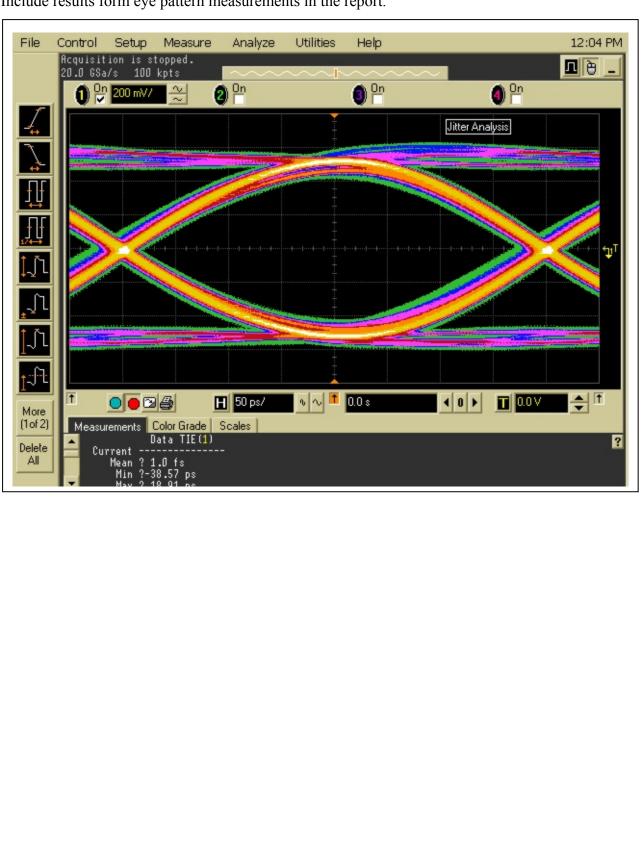

| 8   | 8.7.                   | EYE PATTERN MEASUREMENT                     |                                         |          |              |

| 9.  | DOC                    | UMENTATION                                  | ••••••••••••••••••••••••••••••••••••••• |          | 97           |

| 10  | N                      | 2700G                                       |                                         |          | 00           |

| 10. | N                      | DTES                                        | ••••••••••••••••••••••••••••••          |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        |                                             |                                         |          |              |

|     |                        | Document No.                                | Revision                                | Date     |              |

|     | п                      | 000002H-spec.doc                            | 1.5                                     | 08/09/06 | Page 5 of 24 |

## **TABLE OF FIGURES**

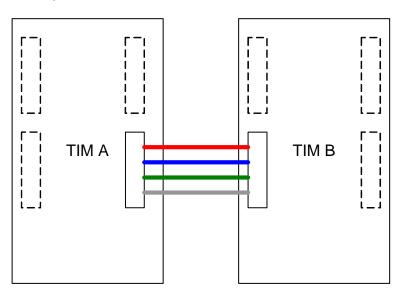

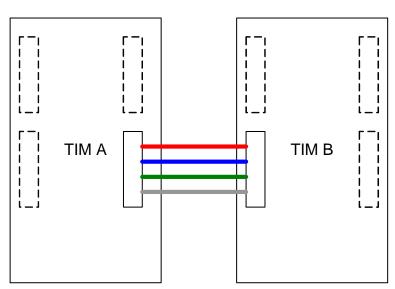

| Figure 1: 4 lanes connection between 2 TI                      | Ms                |          | 14           |  |

|----------------------------------------------------------------|-------------------|----------|--------------|--|

| Figure 2: Basic channel model for chip-to-                     | chip application  | 5        | 16           |  |

| Figure 3: Basic channel model for module-to-module application |                   |          |              |  |

| Figure 4: Basic channel model for Copper                       | cable application | r        | 17           |  |

| Figure 5: Basic channel model for optical of                   | cable application |          | 17           |  |

| Figure 6: RSL QSE-014-xx-DP Type Conne                         | ector             |          | 21           |  |

| Figure 7: RSL QTE-014-xx-DP Type Conn                          | ector             |          | 21           |  |

| Figure 8: Location of RSL Connectors on T                      | Top of a TIM Mo   | dule     | 23           |  |

| Figure 9: Location of RSL Connectors on E                      | Bottom of a TIM   | Module   | 23           |  |

| Figure 10: Location of RSL Connectors on                       | Carrier TIM Site  | 2        | 24           |  |

| Figure 11: Joining two adjacent TIM modu                       | ıles              |          | 25           |  |

| Figure 12: RSL High Speed Data Link Cab                        | le                |          | 25           |  |

| Figure 13: RSL Naming Convention                               |                   |          |              |  |

| Figure 14: Top and Bottom RSL Connector on TIM Module          |                   |          |              |  |

| Figure 15: RSL Connection between TIM M                        | Nodule and Carr   | ier      |              |  |

| Figure 16: Rigid PCB Pin Assignments                           |                   |          | 40           |  |

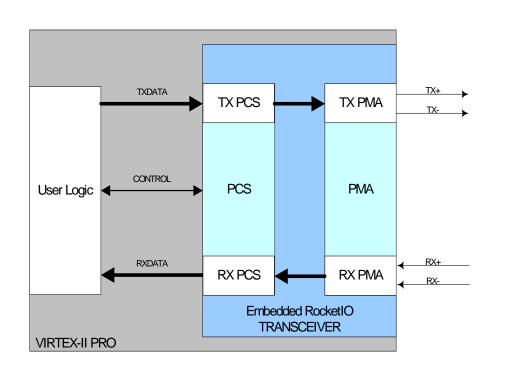

| Figure 17: Basic transceiver model                             |                   |          | 43           |  |

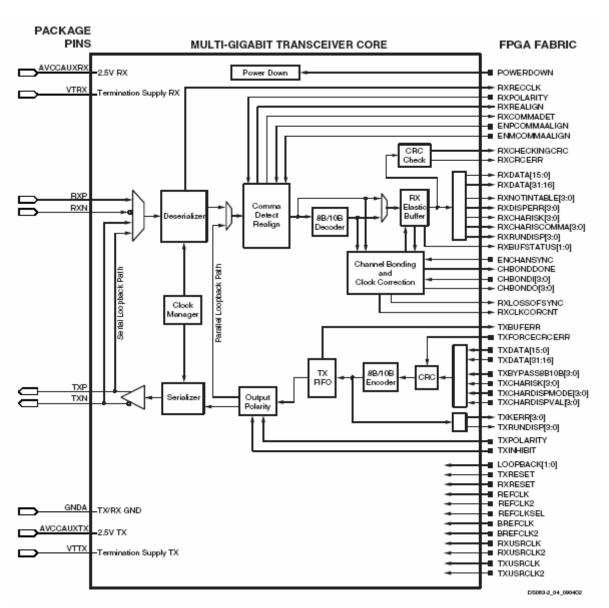

| Figure 18: The Xilinx Multi-Gigabit Transo                     | ceiver Core       |          | 47           |  |

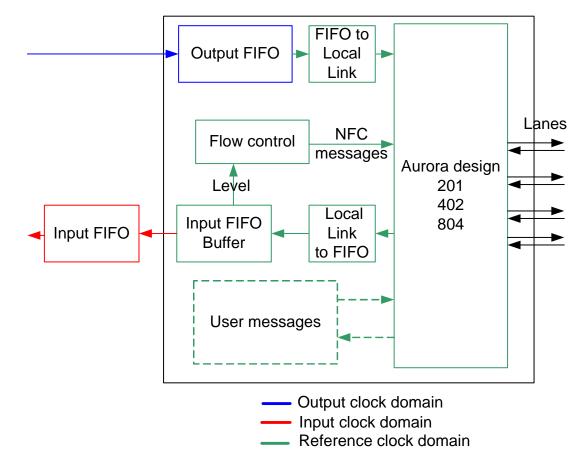

| Figure 19: Top-level design - Subsystem br                     | eakdown           |          | 51           |  |

| Figure 20: MGT Differential Driver                             |                   |          | 63           |  |

| Figure 21: MGT differential Receiver                           |                   |          | 64           |  |

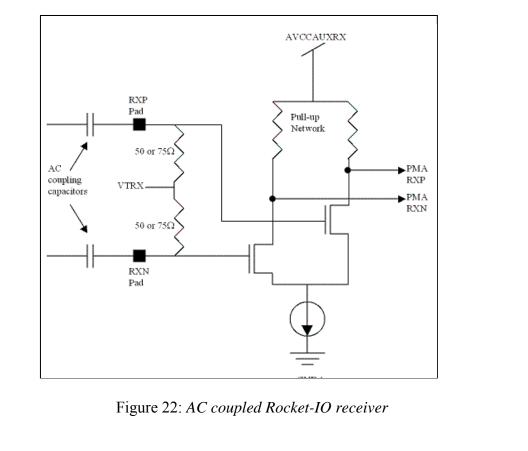

| Figure 22: AC coupled Rocket-IO receiver                       |                   |          | 65           |  |

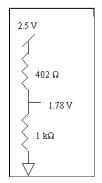

| Figure 23: Voltage divider                                     |                   |          | 66           |  |

| Figure 24: Test layout for the RSL link                        |                   |          | 68           |  |

| Figure 25: Test layout for the RSL interface                   | e                 |          | 69           |  |

|                                                                |                   |          |              |  |

|                                                                |                   |          |              |  |

| Document No.                                                   | Revision          | Date     | Page 6 of 24 |  |

| D000002H-spec.doc                                              | 1.5               | 08/09/06 |              |  |

## 1. SCOPE

This document specifies the requirements for the implementation of the Sundance Rocket-IO Serial Link (RSL).

Sundance's move towards RSL aims at:

- Decreasing costs by decreasing the pin count

- Simplifying connectivity solutions by replacing the various parallel interfaces with various bus sizes used up to now by RSL links instead

- Decreasing support by using industry standard protocols and cores for serial links

As a result, the flow of data will be optimised, potential bottlenecks decreased or even eliminated and compatibility with the rest of the industry improved.

The TIM modules created will be a new range of modules with no backward compatibility options with existing TIM modules communication interfaces.

This document describes various aspects of the Rocket Serial Link (RSL). It covers the mechanical specifications for the standard, including the connector types, position and pin-outs. It covers the hardware characteristics of the interconnection standard as well as certain standard hardware building blocks.

#### **1.1. INTRODUCTION**

The Rocket-IO Serial Link (RSL) is a serial interconnection standard that is capable of data transfer speeds of up to 2.5Gbit/s per serial link (i.e. up to 250MB/s over one serial link). Up to four of these links can be combined to form a Rocket-IO Serial Link Communications Channel that is capable of data transfer up to 10Gbit/s.

Each RSL is made up of a differential Transmitter and Receiver pair. A single Rocket-IO Serial Link is a full-duplex link and can transfer data at up to 2.5Gbit/s in either direction at the same time. The transmission clock is recovered from the data stream, leaving the link as a fully independent communications link that requires no additional control or data signals.

The RSL standard is based on the Rocket-IO transceiver core embedded on Xilinx Virtex-II Pro and Virtex-4 FPGAs.

These silicon integrated transceiver cores handle the serialization/deserialization of the data streams as well as certain low-level management functions.

Rocket-IO transceivers have flexible features and allow serial transmissions over a wide range of serial standards, which require Sundance to define a framework for their use.

The RSL specification defines all the aspects of how to interconnect Sundance modules in a standard way using the integrated Rocket-IO transceivers in the Xilinx Virtex-II Pro devices. The Rocket-IO transceivers are not limited for use with Sundance RSL compliant hardware only. These transceivers, with adequate physical layers, may be used form many different serial interconnection standards. For instance, these standards include Rapid-IO, Infiniband, Serial ATA and Gigabit Ethernet.

| Document No.      | Revision | Date     | Page 7 of 24  |

|-------------------|----------|----------|---------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 7 01 24 |

#### **1.2. PURPOSE**

Sundance wants to reduce system complexity and increase overall speed performances by using the Rocket-IO of the Xilinx FPGAs as the main communication media between TIM modules or/and carrier boards.

#### **1.3. APPLICABILITY**

Any hardware module with a Virtex-II/Pro and a Virtex-4 FPGA device, and RSL connectors should respect these specifications.

| Document No.      | Revision | Date     | Page 8 of 24  |

|-------------------|----------|----------|---------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 0 01 24 |

## 2. APPLICABLE DOCUMENTS AND REFERENCES

#### 2.1. APPLICABLE DOCUMENTS

#### **2.1.1. External Documents**

- [1] Xilinx Virtex-II pro user guide

- [2] Xilinx Rocket IO transceiver user guide

- [3] <u>Aurora reference design</u>

- [4] Aurora application examples

- [5] <u>Xilinx Virtex-4 user guide</u>

- [6] Xilinx Virtex-4 Rocket-IO Multi-Giga bits Transceivers (MGT)

#### 2.1.2. Internal documents

- D000052-spec

- D000049H-spec

- D000049H-veri

- D000049H-impl

- RSL pinouts

- RSL Technical specification Rev01 Iss03

#### 2.1.3. Project Documents

• Master design project.mpp

#### 2.2. **REFERENCES**

#### 2.2.1. External documents

N.A

2.2.2. Internal documents

N.A

#### 2.2.3. Project documents

N.A

| Document No.      | Revision | Date     | Page 9 of 24  |

|-------------------|----------|----------|---------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 9 01 24 |

#### **2.3. PRECEDENCE**

In the event of conflict between the text of this document, and the applicable documents cited herein, the text of this document takes precedence. Nothing in this document however, supersedes applicable laws and regulations unless a specific exemption has been obtained and is identified in the text of this document.

| Document No.      | Revision | Date     | Page 10 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 uge 10 01 24 |

## 3. ACRONYMS, ABBREVIATIONS AND DEFINITIONS

#### 3.1. ACRONYMS AND ABBREVIATIONS

- TIM Texas Instruments Module

- RSL Rocket-IO Serial Link

- MGT Multi-Gigabit Serial Transceiver

- XAUI 10 Gigabit Attachment Unit Interface

- PHY Physical Layer

- PMA Physical Media Attachment

- PCS Physical Coding Sub layer

| Document No.      | Revision | Date     | Page 11 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 11 01 24 |

#### **3.2. DEFINITIONS**

| Rocket-IO              | Rocket-IO is                                                                                                                                                                                                                                                                                                                                                          | s the name given   | to a multi-gigabit    | serial transceiver (MGT) |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|--------------------------|--|--|--|--|

|                        |                                                                                                                                                                                                                                                                                                                                                                       |                    | x Virtex-II Pro dev   |                          |  |  |  |  |

| XAUI                   | Pronounced "Zowie". The "AUI" portion is borrowed from the Ethernet<br>Attachment Unit Interface. The "X" represents the Roman numeral for<br>ten and implies ten gigabits per second. The XAUI is designed as an<br>interface extender, and the interface, which it extends, is the XGMII, the<br>10 Gigabit Media Independent Interface. <u>Detailed definition</u> |                    |                       |                          |  |  |  |  |

| РНҮ                    | The PHY is the lowest layer within the OSI Network Model. It dea<br>primarily with transmission of the raw bit stream over the physic<br>transport medium.                                                                                                                                                                                                            |                    |                       |                          |  |  |  |  |

|                        | The PHY co<br>encoded data                                                                                                                                                                                                                                                                                                                                            |                    | ions that transmit,   | receive and manage the   |  |  |  |  |

| Differential voltage   | The differen                                                                                                                                                                                                                                                                                                                                                          | tial voltage acros | s the circuit pair is | the desired signal       |  |  |  |  |

| Common Mode<br>Voltage | The voltage common to both sides of a differential circuit pair. The common voltage signal is the unwanted signal that may have been coupled into the transmission line. If the line is perfectly balanced, the common mode voltage cancels out. The degree of cancellation is called the <u>common mode rejection ratio</u> , or <u>CMRR</u> .                       |                    |                       |                          |  |  |  |  |

| AC coupling            | Use of a special circuit to remove the static (DC) components from the input signal to the <u>amplifier</u> in an instrument, leaving only the components of the signal that vary with time.                                                                                                                                                                          |                    |                       |                          |  |  |  |  |

| Pre-emphasis           | In pre-emphasis, the initial differential voltage swing is boosted to create<br>a stronger rising or falling waveform. This method compensates for high<br>frequency loss in the transmission media that would otherwise limit the<br>magnitude of this waveform.                                                                                                     |                    |                       |                          |  |  |  |  |

| PCS                    | The PCS is t                                                                                                                                                                                                                                                                                                                                                          | he FPGA fabric     | data interface of the | e Rocket-IO transceiver  |  |  |  |  |

| РМА                    | The PMA is                                                                                                                                                                                                                                                                                                                                                            | the Rocket-IO tr   | ansceiver physical    | interface.               |  |  |  |  |

| DC balanced            | A channel is said to be DC Balanced if it has an equal number of 1's and 0's transmitted across it. Encoding schemes like 8B/10B are designed to ensure this.                                                                                                                                                                                                         |                    |                       |                          |  |  |  |  |

| DC coupling            | Method of interfacing drivers and receivers without the use of series capacitors. A direct connection (through PCB trace) from driver to receiver.                                                                                                                                                                                                                    |                    |                       |                          |  |  |  |  |

| AC coupling            | Method of interfacing drivers and receivers through a series capacitor.<br>Often used when the differential swing between drivers and receivers is<br>compatible, but common mode voltages of driver and receiver are not.<br>Requires that a minimum data frequency be established based on the RC<br>time constant, necessitating a run length limit.               |                    |                       |                          |  |  |  |  |

| Document No.           |                                                                                                                                                                                                                                                                                                                                                                       | Revision           | Date                  | Page 12 of 24            |  |  |  |  |

| D000002H-spec          | .doc                                                                                                                                                                                                                                                                                                                                                                  | 1.5                | 08/09/06              | 1 ugo 12 01 27           |  |  |  |  |

|                        |                                                                                                                                                                                                                                                                                                                                                                       |                    |                       |                          |  |  |  |  |

### 4. REQUIREMENTS

#### 4.1. PRIME ITEM DEFINITION

The Rocket-IO provides high speed, serial, point-to-point communication channels within a Sundance system.

The speed over one serial channel can vary:

- From 600Mbits/s up to 3.125Gbits/s for Virtex-II FPGAs

- From 622Mbits/s up to 10.3125Gbits/s for the Virtex-4 FPGAs

Many serial protocols can be implemented using Rocket-IO technology, and none of these new serial standards are expected to out perform all of the others.

The next part of this document characterizes Sundance's current systems communication channels and derives basic communication models for the RSL.

Then, we need to review the major serial communication standards applicable to transfer in these configurations and conclude on feasibility and limitations for Sundance systems.

Finally, clear specifications can be derived so that Sundance can build reliable and compatible systems based on Rocket-IO serial transmissions.

The RSL features are:

- Full duplex communication per RSL

- Data transfer at up to 2.5Gbit/s per RSL

- Grouping of up to four RSL to form a single 10Gbit/s link

- Low voltage differential signalling (LVDS) used

- Full clock recovery from data stream

- Compatibility with emerging serial interconnection standards

#### 4.1.1. Prime Item Diagrams

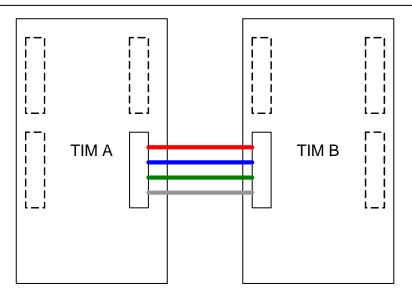

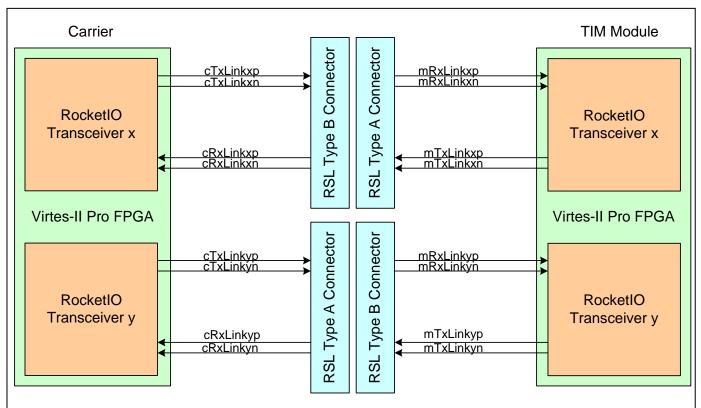

The system is going to be made of two TIMs performing transfers over the RSL using the Aurora interface. Each RSL can be built with a number of lanes. Each lane is made of two differential pairs, one to receive and one to send.

The lanes can be independent or bonded for higher transfer rates.

| Decument No.      | Davision | Data     |               |

|-------------------|----------|----------|---------------|

| Document No.      | Revision | Date     | Page 13 of 24 |

| D000002H-spec.doc | 1.5      | 08/09/06 | 5             |

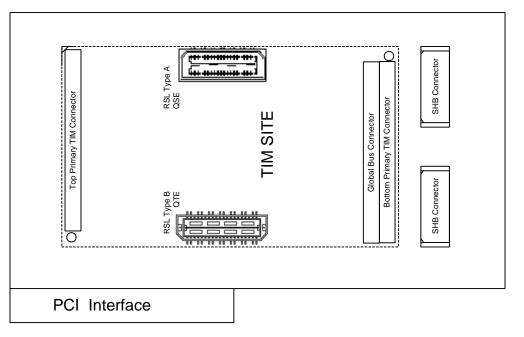

Figure 1: 4 lanes connection between 2 TIMs

#### **4.1.2.** Interface Definition

The interface is based on Xilinx's Aurora protocol that is fully described by them.

On one side is the serial interface going to the next TIM and on the other side is the user interface, which is a standard interface as well from Xilinx, called the Local Link interface. It is as well fully specified by Xilinx.

#### 4.1.3. Major Component List

The elements to consider in the design are:

- Virtex-II/Pro, hardware design to support RSL (power supply, clocks etc...)

- Board interconnections (connectors, cable)

- Aurora interfaces to serial links

- User interfaces to Local Link

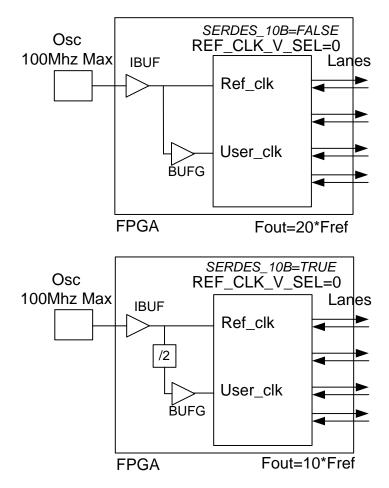

#### 4.1.4. Prime item characteristics

Clock rates

#### 4.1.5. Performances

Performances depend on few things:

• Reference clock rates as the data is transferred at (clock\_rate\* 20 / 10) MB/s

Explanations: /10 because of 8B/10B encoding

- FIFO size, which is directly related to interface latency and flow control

- Number of lanes used for the transfer (data width)

| Document No.      | Revision | Date     | Page 14 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 450 14 01 24 |

#### • Speed supported by the interconnection

| So with optimum FIFO size, the performances should be as follows. |         |         |          |  |  |  |  |

|-------------------------------------------------------------------|---------|---------|----------|--|--|--|--|

|                                                                   | 1 lane  | 2 lanes | 4 lanes  |  |  |  |  |

| 100 MHz Ref clock (2Gb/s)                                         | 200Mb/s | 400Mb/s | 800Mb/s  |  |  |  |  |

| 125 MHz Ref clock (2.5Gb/s)                                       | 250Mb/s | 500Mb/s | 1000Mb/s |  |  |  |  |

| 156.25 MHz Ref clock (3.125Gb/s)                                  | 312Mb/s | 624Mb/s | 1248Mb/s |  |  |  |  |

So with optimum FIFO size, the performances should be as follows:

The maximum speed over a serial link depends on the standard implemented.

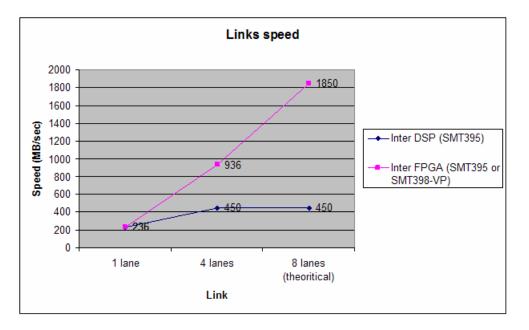

Speed test figures:

Those figures report the speed test done by Sundance on the RSL links.

The modules used are the SMT395VP30 and the SMT398VP70.

They show that the maximum performance that the RSL can sustain is 450MB/s inter DSP when grouped by 4 lanes and 936MB/s inter FPGA in the same conditions.

| Document No.      | Revision | Date     | Page 15 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 15 01 24 |

#### 4.2. SUNDANCE RSL MODELS

This section gives detailed description of the model of the RSL.

#### 4.2.1. Current communications within Sundance systems

The current communications within Sundance systems can take place between:

- Chips on a module: like DSP / FPGA

- Modules on a carrier board, (also including between a module and its carrier board)

- Modules on different carrier boards in the same chassis, (can be front panel to front panel or direct modules inter-connections)

- Equipments or chassis

#### 4.2.2. RSL communications within Sundance systems

So, in theory, the Rocket-IO serial link can be used in any of the combinations listed above.

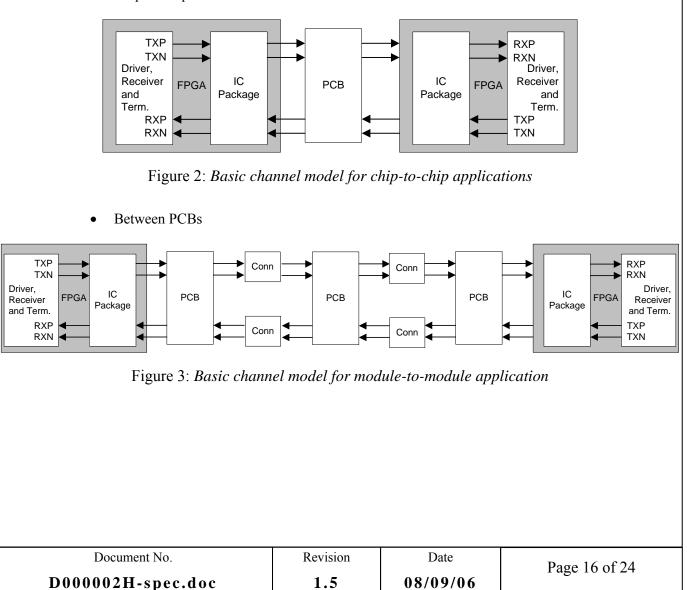

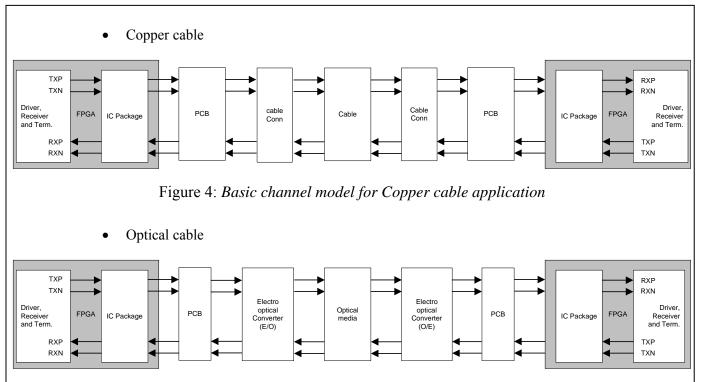

We can derive four basic categories from the above communication channels:

• Chip-to-chip

Figure 5: Basic channel model for optical cable application

An overview of these four basic models is available from Xilinx in "<u>Usage Models for Multi-Gigabit serial transceivers</u>".

All of these four categories always include the FPGA as the essential part of the system.

Then more elements are involved depending on the distance to cover:

- Connectors

- Cables

- Optical fibers

- Passive/Active components

#### 4.2.3. RSL protocol

Sundance wants to be as flexible as possible and support as many protocols as possible. The protocols used depend on the application/system and different protocols could be used on the same module. For the module-to-module communications in the previous models Sundance implements an Aurora protocol in its FPGA firmware.

#### 4.2.4. Basic protocols and IO rates

The next table includes specific baud rates used by the standards supported by the Rocket-IO transceiver.

| Document No.      | Revision | Date     | Page 17 of 24 |

|-------------------|----------|----------|---------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | Page 17 of 24 |

| Mode                    | Channels   | IO bit rate (Gb/s) |  |  |

|-------------------------|------------|--------------------|--|--|

| Fiber Channel           | 1          | 1.06               |  |  |

|                         |            | 2.12               |  |  |

| Gigabit Ethernet        | 1          | 1.25               |  |  |

| XAUI (10 Gbit Ethernet) | 4          | 3.125              |  |  |

| Infiniband              | 1, 4, 12   | 2.5                |  |  |

| Aurora                  | 1, 2, 3, 4 | 0.600-3.125        |  |  |

| Custom                  | 1, 2, 3, 4 | 0.600-3.125        |  |  |

Table 1: Protocols supported by the Rocket-IO transceiver

Each of these protocols uses its specific IO bit rate, which is NOT the same as the effective data rate as data needs to be encoded/decoded in most cases.

Encoding data guarantees a DC-balanced, edge-rich serial stream, facilitating DC-or AC-coupling and clock recovery.

The FPGA Rocket-IO supports 8B/10B encoding/decoding therefore the effective data rate is 4/5 of the actual IO bit rate.

Detailed information is available in <u>Xilinx Rocket IO transceiver User guide</u> section "8B/10B Encoding/Decoding" in Chapter 2. (page 63)

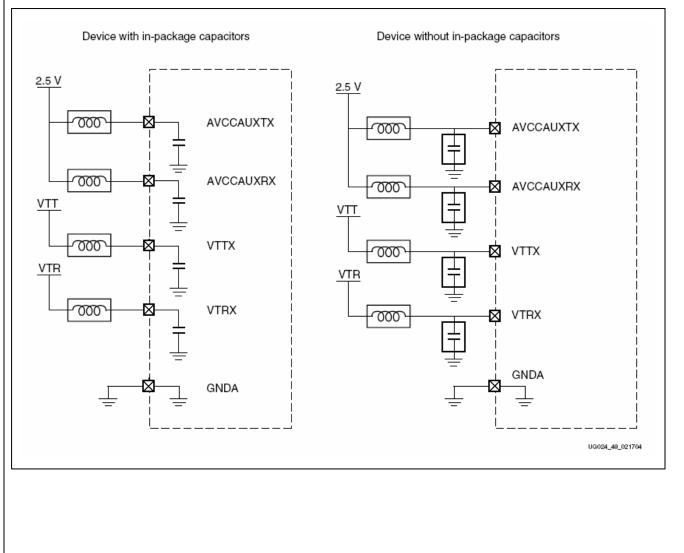

#### 4.2.5. RSL features

The choice of Virtex-II PRO to be fitted on-board is CRUCIAL as it determines:

- The amount of Rocket IO channels available for serial transfers

- Whether a power filtering capacitor is internal to the FPGA or must be added onboard

- The maximum serial speed

| Document No.      | Revision Date |          | Page 18 of 24  |

|-------------------|---------------|----------|----------------|

| D000002H-spec.doc | 1.5           | 08/09/06 | 1 uge 10 01 24 |

|                        | am  | ount of a | available  | Rocket- | IO trans   | ceivers j | per device | eed grade<br>e, the maxi<br>to the pack | imum spe   |        |        |

|------------------------|-----|-----------|------------|---------|------------|-----------|------------|-----------------------------------------|------------|--------|--------|

|                        |     |           | Internal   | power f | iltering o | capacitor | r          | FG packa                                | ges        |        |        |

|                        |     |           | Externa    | l power | filtering  | capacito  | or         | FF packag                               | ges        |        |        |

| Table 2: Colour scheme |     |           |            |         |            |           |            |                                         |            |        |        |

| FPGA speed             | -5  |           | 2.0 Gb/s   |         |            |           |            | 2.0 Gb/s                                |            |        |        |

| grade                  | -6  | 2.5 Gb/s  |            |         |            |           |            | 3.125 Gb/                               | ′s         |        |        |

|                        | -7  | 2.5 Gb/s  |            |         | 3.125 Gb/s |           |            |                                         |            |        |        |

| MGT per devi           | ce  | FG256     | FG456      | FG676   | FF672      | FF896     | FF1152     | FF1148                                  | FF1517     | FF1704 | FF1696 |

| XC2VP2                 |     | 4         | 4          |         |            |           |            |                                         |            |        |        |

| XC2VP4                 |     | 4         | 4          |         |            |           |            |                                         |            |        |        |

| XC2VP7                 |     |           | 4          |         | 8          | 8         |            |                                         |            |        |        |

| XC2VP20                |     |           |            | 8       |            | 8         | 8          |                                         |            |        |        |

| XC2VP30                |     |           |            | 8       |            | 8         | 8          |                                         |            |        |        |

| XC2VP40                |     |           |            | 8       |            |           | 12         | No MGT                                  |            |        |        |

| XC2VP50                |     |           |            |         |            |           | 16         | No MGT                                  | 16         |        |        |

| XC2VP70                |     |           |            |         |            |           |            |                                         | 16         | 20     |        |

| XC2VP100               | )   |           |            |         | 20 No MGT  |           |            |                                         |            |        |        |

| ]                      | Гab | le 3: Vir | tex-II pro | o FPGA  | Device, j  | package   | speed gro  | ade combir                              | nations fo | r RSL  |        |

Important notes relevant to the table 3:

- Wire bond packages FG256, FG456, and FG676 are also available in Pb-free versions FGG256, FGG456, and FGG676.

- The Rocket-IO transceivers in devices in the FF1148 and FF1696 packages are not bonded out to the package pins (noted No MGT in the table 3).

- -7 speed grade devices are not available in Industrial grade.

| Document No.      | Revision | Date     | Page 19 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | r age 19 01 24 |

• The 2VP30, 2VP40, 2VP50, 2VP70 and 2VP100 have always had the internal capacitors. The 2VP2, 2VP4, 2VP7, and 2VP20 have had the internal capacitors beginning with data code 0317 (17th week of 2003). The date code is the last three numbers of the second line of markings on the part (same line as the package, i.e. FG456)

More detailed information is available in the <u>Xilinx Rocket IO transceiver User guide</u> section "Passive Filtering" in Chapter 3 (page 113).

| MGT per device | SF363 | FF672 | FF668 | FF1148 | FF1152 | FF1513 | FF1517 | FF1760 |

|----------------|-------|-------|-------|--------|--------|--------|--------|--------|

| XC4VFX12       | N/A   |       | N/A   |        |        |        |        |        |

| XC4VFX20       |       | 8     |       |        |        |        |        |        |

| XC4VFX40       |       | 12    |       |        | 12     |        |        |        |

| XC4VFX60       |       | 12    |       |        | 16     |        |        |        |

| XC4VFX100      |       |       |       |        | 20     |        | 20     |        |

| XC4VFX140      |       |       |       |        |        |        | 24     | 24     |

Table 4: Virtex-4 FPGA Device, package combinations for RSL

| Document No.      | Revision | Date     | Page 20 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 20 01 24 |

#### 4.3. MECHANICAL SPECIFICATIONS

This section describes the mechanical specifications of the RSL connectors (the orientation, connector type).

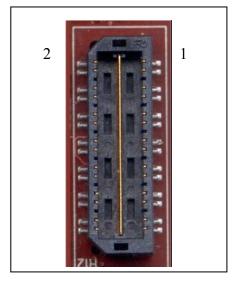

#### 4.3.1. Connector type

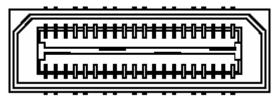

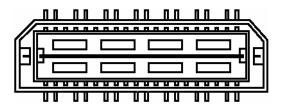

The RSL connectors used on the TIM modules and carrier boards are 0.8mm pitch differential Samtec connectors. Any single connector makes provision for a maximum of 14 differential pairs. The Samtec QSE-014-xx-DP and QTE-014-xx-DP type of connectors are used on both the TIM modules and the Carriers.

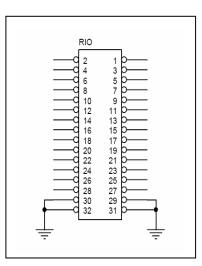

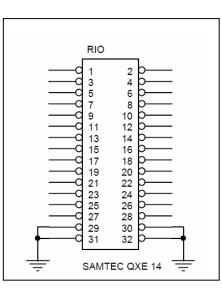

The following two diagrams show the Top View of the QSE and QTE type connectors.

Figure 6: RSL QSE-014-xx-DP Type Connector

Figure 7: RSL QTE-014-xx-DP Type Connector

Both connectors have a single pin omitted on either side of the connector after every second pin. This architecture creates 14 individual differential pairs in the connector with proper isolation between pairs. The connector also contains a solid integrated ground plain in the middle throughout the full length of the connector. This provides addition shielding to the differential pairs. The connector characteristics for a 5.03mm QSE/QTE connector stack is given in the following table:

| Impedance    | Impedance Mismatch (Ohm) |      |           | Cross Talk        |

|--------------|--------------------------|------|-----------|-------------------|

| Period       | Impeda                   | ance | Frequency | Percentage        |

| 30 ps        | 111.6 to                 | 88.0 | 6.40 GHz  | ~1.75%            |

| 50 ps        | 103.6 to                 | 94.0 | 10.00 GHz | ~2.0%             |

| 100 ps       | 98.8 to                  | 98.2 |           |                   |

| 250 ps       | 100.0 to                 | 99.6 |           |                   |

|              | Table 5: QSE / QTE C     |      |           |                   |

|              |                          |      |           |                   |

|              |                          |      |           |                   |

| Document No  | Document No.             |      | Date      | Page 21 of 24     |

| D000002H-spe | ec.doc                   | 1.5  | 08/09/06  | 1 4 5 2 1 0 1 2 1 |

The connectors are keyed to ensure correct insertion. The default QSE/QTE stacking height is 5.03 mm. The following stacking heights are also available: 8.03mm, 11.03mm, 16.00mm, 19.00mm, and 22.00mm. The QSE connector always stays the same height. The QTE connector determines the stacking height.

The table underneath list the preferred TIM module and Carrier connector part numbers for a stacking height of 5.03mm. A description of which connectors are used where is provided in the following section.

| No | Connector Description                | Document Reference | Samtec Part Number  |  |

|----|--------------------------------------|--------------------|---------------------|--|

| 1  | TIM and Carrier RSL Type A Connector | QSE-014-xx-DP      | QSE-014-01-F-D-DP-A |  |

| 2  | TIM and Carrier RSL Type B Connector | QTE-014-xx-DP      | QTE-014-01-F-D-DP-A |  |

|  | Table 6: | Full RSL | Connector | Part Numbers |

|--|----------|----------|-----------|--------------|

|--|----------|----------|-----------|--------------|

For more information about the QSE-014-xx-DP or QTE-014-xx-DP connectors please visit the <u>Samtec</u> website.

#### **4.3.2.** Connector location

Unlike the SHB, the RSL signals are not bi-directional. To prevent inadvertent connection from Tx-to-Tx (and Rx-to-Rx), different connector genders with different signal assignments are used.

There are two sets of signal assignments: RSL Type A (uses the Samtec *QSE-014-01-F-D-DP-A* connector) and RSL Type B (uses the Samtec *QTE-014-01-F-D-DP-A* connector). When interconnecting RSL pairs RSL Type A must always interface to RSL Type B and visa versa. *Note: It is however possible for similar connectors in the same group to have different pin-outs, depending on the connectors location.*

A connecting cable will therefore have a different gender at each end, and also be a straight one-to-one connection.

A single RSL is bi-directional. The RSL Type A signal group and the RSL Type B signal group thus contains a certain amount of bi-directional links each. RSL Type A links should NOT be confused as outputs only and RSL Type B links as inputs only.

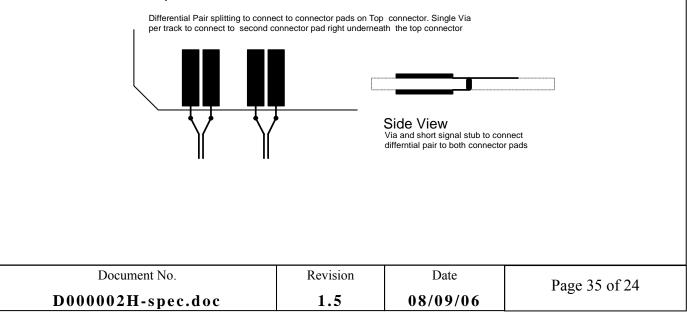

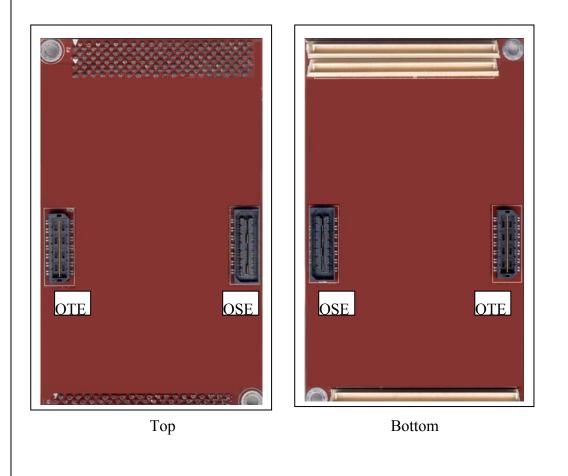

If the TIM board space permits, an additional connector should be fitted on the underside of the module, directly beneath the connector on the top. The underside connector should have the same gender as the corresponding one on top. Connectivity is such that a single via should allow connection to both pins. So that pin 1 (top) will connect to pin 27 (bottom) and so on.

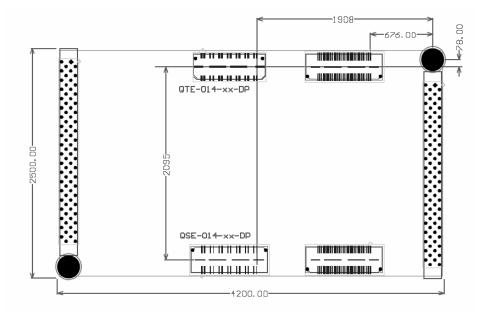

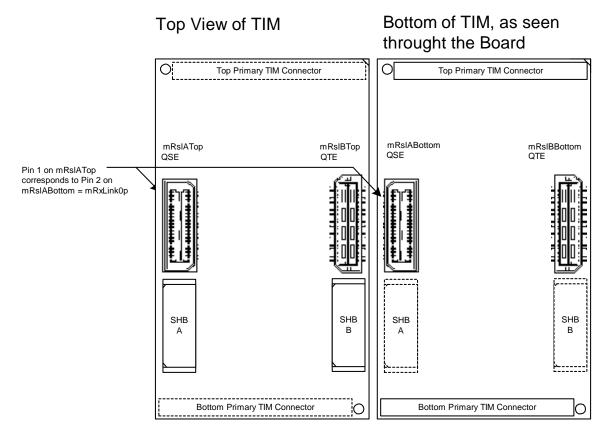

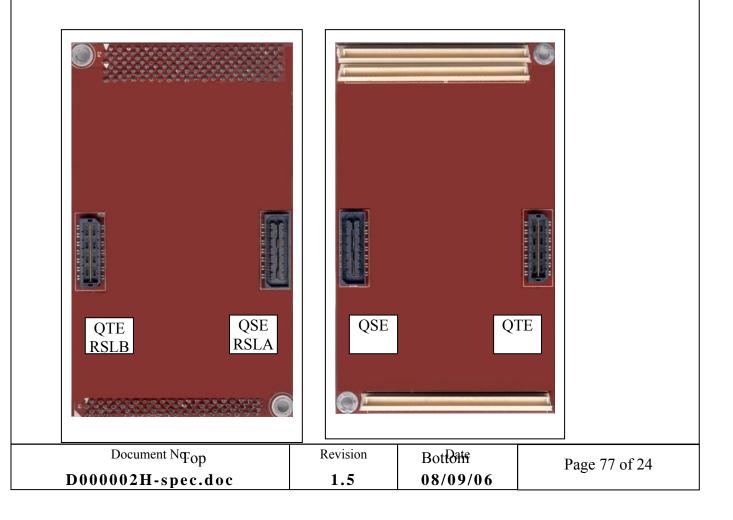

#### 4.3.2.1. Compliant TIM module

On a TIM module the RSL connectors replace the optional second set of SHB connectors. Next to the SHB-A connector the RSL Type A connector is located. This connector is a QSE-014-xx-DP type connector. Next to the SHB-B connector the RSL Type B connector is located. This connector is a QTE-014-xx-DP type connector. These two connectors are located on the Top of the TIM Module and are ideal for module-to-module inter-connection. Identical connectors, but with a different pin-out, are located right underneath the RSL Type

| Document No.      | Revision | Date     | Page 22 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 22 01 24 |

A and RSL Type B connectors. This set of connectors makes it possible to connect a RSL between a TIM module and a carrier without having to route the signals through a cable.

A TIM module thus contains two sets of two RSL connectors. Each set contains one connector on the Top of the module, and one on the Bottom of the module. The RSL Type A connector is a QSE type connector, and the RSL Type B connector is a QTE connector.

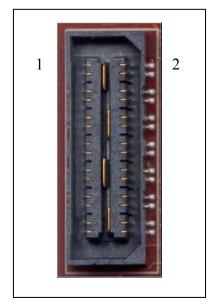

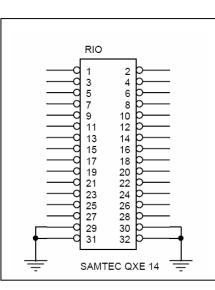

The following two diagrams show the exact location of the RSL Type A and RSL Type B connectors on the Top and Bottom of a TIM module.

Figure 8: Location of RSL Connectors on Top of a TIM Module

Figure 9: Location of RSL Connectors on Bottom of a TIM Module

| Document No.      | Revision | Date     | Page 23 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 460 25 01 21 |

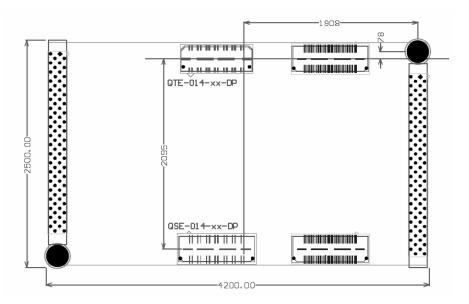

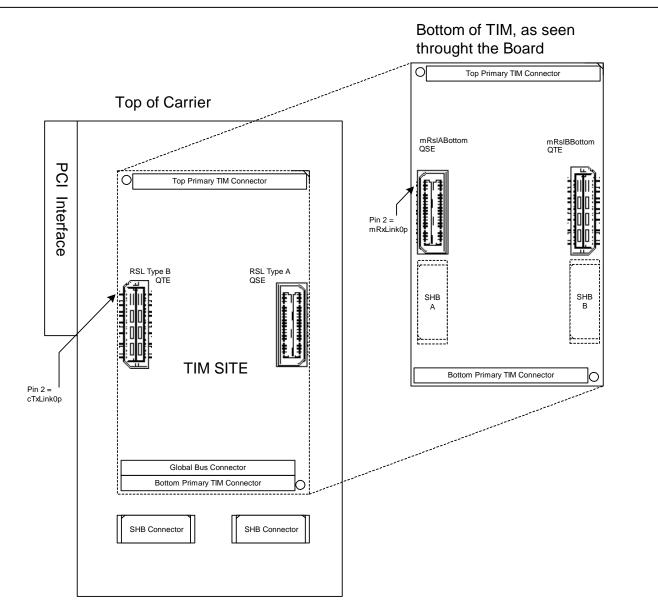

#### 4.3.2.2. Compliant TIM carrier boards

All RSL compliant carrier boards contain only two RSL connectors per TIM site. There is one RSL Type B QTE connector to mate with the RSL Type A QSE connector on the TIM module. And there is one RSL Type A QSE connector to mate with the RSL Type B QTE connector.

The exact mechanics of the connector placement may vary according to the type of the carrier board. For this reason only a diagram depicting the location of the RSL Type A and B Connectors in relation to the TIM site is shown in the following diagram:

Figure 10: Location of RSL Connectors on Carrier TIM Site

Future RSL compliant carrier boards may expand the RSL standard to include industry standard connectors for interfaces such as Rapid-IO, SATA, Infiniband and Gigabit Ethernet. In general the design impact of conforming to one of the above-mentioned standards is very small on the hardware side, but rather large on the firmware and software side. The Xilinx Virtex-II Pro Rocket-IO transceivers and Virtex-4 Rocket-IO MGT are compatible with the above-mentioned standards.

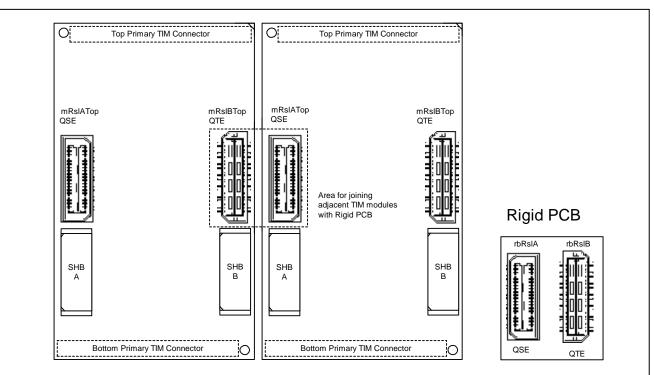

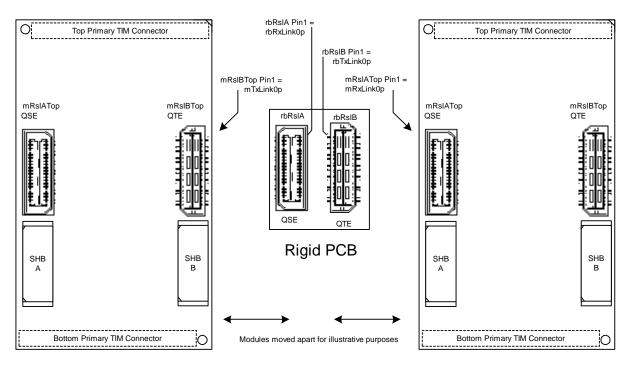

#### 4.3.3. Rigid Printed Circuit Boards

Rigid Printed Circuit Boards may be used to interconnect two adjacent TIM Modules. When two TIM modules are placed side by side the RSL Type A connector from the one module is adjacent to the RSL Type B connector form the other. The Rigid PCB provides a RSL Type Ato-Type B bridge between the two modules. The Rigid PCB contains a RSL Type B connector to connect to the Module RSL Type A connector and visa-versa. The routing on the PCB is a straight through one-to-one routing.

The two following diagrams illustrate this concept. The notation used to describe the location and type of connector is explained in the following section: 4.3.5.

| Document No.      | Revision | Date     | Page 24 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 24 01 24 |

Figure 11: Joining two adjacent TIM modules

The above diagram illustrates the area for joining two adjacent TIM modules with a Rigid PCB. The diagram above illustrates the rigid PCB.

Note: on the rigid PCB a RSL QSE Type B connector mates with the TIM module RSL QTE Type A connector.

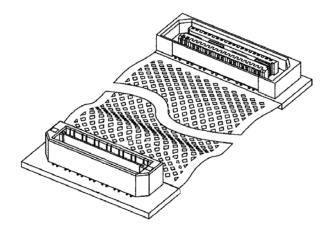

#### 4.3.4. Cables

It is also possible to connect a RSL Type A connector to a RSL Type B connector using a highspeed flexible cable with a QTE connector on the one side and a QSE connector on the other side. Like the rigid PCB the cable is a straight through one-to-one cable.

Figure 12: RSL High Speed Data Link Cable

The matching cable for the RSL Type A and Type B connectors is the Samtec High Speed Data Link Cable (HFEM Series). An illustration of this cable is shown the in figure 12 above. The cable comes in three lengths, measured from the outer edges of both connectors. These lengths are 76.2mm, 127.0mm and 242.32mm. The main characteristics of the cable are:

| Document No.      | Revision | Date     | Page 25 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 25 01 24 |

| Inserti   | Insertion Loss |            | Impedance (Ohm) |  |  |

|-----------|----------------|------------|-----------------|--|--|

| Frequency | Loss           | Frequency  | Percentage      |  |  |

| 500 MHz   | -0.7 dB        | Full Range | +/- 10%         |  |  |

| 1.0 GHz   | -1.2 dB        |            |                 |  |  |

| 1.5 GHz   | -1.3 dB        |            |                 |  |  |

| 2.0 GHz   | -2.2 dB        |            |                 |  |  |

| 2.5 GHz   | -2.2 dB        |            |                 |  |  |

| 3.0 GHz   | -2.5 dB        |            |                 |  |  |

| 3.5 GHz   | -3.4 dB        |            |                 |  |  |

Table 7: *HFEM cable characteristics*

#### 4.3.5. Connector type/location

A unique identifier is assigned to each possible position. It is recommended that this identifier or similar identification appears in all RSL schematics to help with identifying the connector Type and Location.

| No | Location                      | RSL<br>Connector |                                          | Location             | Identifier    | Part Nber         |

|----|-------------------------------|------------------|------------------------------------------|----------------------|---------------|-------------------|

| 1  | Carrier                       | Type A           | TIM s                                    | ite on Carrier       | cRslA         | QSE-014-xx-<br>DP |

| 2  | Carrier                       | Туре В           | TIM s                                    | ite on Carrier       | cRslB         | QTE-014-xx-<br>DP |

| 3  | TIM Module                    | Type A           | Top of                                   | f TIM Module         | mRslATop      | QSE-014-xx-<br>DP |

| 4  | TIM Module                    | Type A           | Bottor                                   | n of TIM Module      | mRslABot      | QSE-014-xx-<br>DP |

| 5  | TIM Module                    | Туре В           | Top of TIM Module                        |                      | mRslBTop      | QTE-014-xx-<br>DP |

| 6  | TIM Module                    | Туре В           | Bottom of TIM Module                     |                      | mRslBBot      | QTE-014-xx-<br>DP |

| 7  | RSL Cable                     | Type A           | Module-to-Module or<br>Module-to-Carrier |                      | icRslA        | QSE-014-xx-<br>DP |

| 8  | RSL Cable                     | Туре В           | Module-to-Module or<br>Module-to-Carrier |                      | icRslB        | QTE-014-xx-<br>DP |

| 9  | Module-to-Module Bridging PCB | Type A           | Rigid                                    | Module-to-Module PCB | rbRslA        | QSE-014-xx-<br>DP |

| 10 | Module-to-Module Bridging PCB | Туре В           | Rigid                                    | Module-to-Module PCB | rbRslB        | QTE-014-xx-<br>DP |

|    |                               |                  |                                          |                      |               |                   |

|    | Document No.                  | Revisi           | on                                       | Date Dage 2          |               | 5 of 24           |

|    | D000002H-spec.doc             | 1.5              | 5 08/09/06                               |                      | Page 26 of 24 |                   |

Table 8: RSL Connector Type and Position

The prefix in the Identifier column in the table above helps to identify and locate the specific RSL connector/location that is referred to. The following table summarizes the use of the prefix:

| No | Prefix | Abbreviation For       | Usage Example                                                                            |

|----|--------|------------------------|------------------------------------------------------------------------------------------|

| 1  | ʻc'    | Carrier                | cRslA = RSL Type A connector located on carrier                                          |

| 2  | ʻm'    | Tim Module             | mRslBTop = RSL Type B connector located on the<br>Top of the module                      |

| 3  | ʻic'   | Inter-connecting Cable | icRslA = RSLType A connector located on a module-<br>to-module flexible cable            |

| 4  | ʻrb'   | Rigid PCB              | rbRslB = RSL Type B connector located on a rigid<br>module-to-module interconnection PCB |

Table 9: RSL Prefix explanation

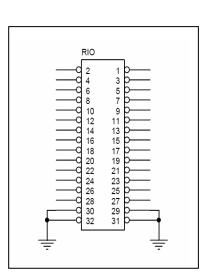

#### 4.4. RSL PINOUTS

This section provides the pinout definitions for the different RSL connectors. The pin-outs vary depending on the RSL Type and the connector location. Depending on the Carrier or TIM module configuration there will always be the four, eight or twelve links available. The amount of links is split over the RSL Type A and RSL Type B connector. So, a module with four links will have two links on the RSL Type A connector and the other two on the RSL Type B connector. Remember that a link is made up out of four signals – a differential Tx pair and a differential Rx pair. The connector pin assignments for all connector locations and the amount of links per connector are provided in the tables in this section.

#### 4.4.1. Naming convention

Each table defines the signal direction as seen from the local perspective of that specific connector. So if the signal name on a RSL Type A connector on a TIM module reads as mRxLink0 it means that it is a signal that is received on the module and thus transmitted from a carrier. The following diagram clarifies this issue:

| Document No.      | Revision | Date     | Page 27 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 27 01 24 |

Figure 13: RSL Naming Convention

The use of the prefix in the signal naming convention is explained in the section titled '*Connector Type/Location*' earlier in this document.

#### 4.4.2. TIM module

The TIM module comes with the most possibilities. The RSL links are routed to an RSL Type A connector and an RSL Type B connector on the Top of the module. The same links are also routed to the same type of connectors underneath the module. This leaves the option open for connecting the links to a carrier, or to an adjacent TIM module. Please note that the links are not multi-drop links and that you can't be connected to a carrier and to another module at the same time. Depending on the size of the FPGA mounted on the module four, eight or twelve links are available. Even thought the same type of connector is used for the RSL Type A and RSL Type B groups on the Top and the Bottom of the module the pin assignments differ. The reasoning behind this is explained in the next section – Carrier Pin Assignments.

#### 4.4.2.1. Connectors pinouts

The next tables list the pin-outs for all of these combinations.

| Document No.      | Revision | Date     | Page 28 of 24  |

|-------------------|----------|----------|----------------|

| D000002H-spec.doc | 1.5      | 08/09/06 | 1 age 20 01 24 |

| 4.4.2.1.1. | <b>RSL type</b> A | , <b>Top</b> , 4 | links, TIM: |

|------------|-------------------|------------------|-------------|

|------------|-------------------|------------------|-------------|

| Pin No | Pin Name  | Signal Description              | Pin No | Pin Name  | Signal Description               |

|--------|-----------|---------------------------------|--------|-----------|----------------------------------|

| 1      | mRxLink0p | Module Receive Link 0, positive | 2      | mTxLink0p | Module Transmit Link 0, positive |

| 3      | mRxLink0n | Module Receive Link 0, negative | 4      | mTxLink0n | Module Transmit Link 0, negative |

| 5      | mRxLink1p | Module Receive Link 1, positive | 6      | mTxLink1p | Module Transmit Link 1, positive |

| 7      | mRxLink1n | Module Receive Link 1, negative | 8      | mTxLink1n | Module Transmit Link 1, negative |

| 9      | Reserved  | Reserved                        | 10     | Reserved  | Reserved                         |

| 11     | Reserved  | Reserved                        | 12     | Reserved  | Reserved                         |

| 13     | Reserved  | Reserved                        | 14     | Reserved  | Reserved                         |

| 15     | Reserved  | Reserved                        | 16     | Reserved  | Reserved                         |

| 17     | Reserved  | Reserved                        | 18     | Reserved  | Reserved                         |

| 19     | Reserved  | Reserved                        | 20     | Reserved  | Reserved                         |

| 21     | Reserved  | Reserved                        | 22     | Reserved  | Reserved                         |

| 23     | Reserved  | Reserved                        | 24     | Reserved  | Reserved                         |

| 25     | Reserved  | Reserved                        | 26     | Reserved  | Reserved                         |

| 27     | Reserved  | Reserved                        | 28     | Reserved  | Reserved                         |

#### 4.4.2.1.2. RSL Type B, Top, 4 Links, TIM

| Pin No | Pin Name  | Signal Description        | Pin No     | Pin Name  | Signal Des | cription               |

|--------|-----------|---------------------------|------------|-----------|------------|------------------------|

| 1      | mTxLink0p | Module Transmit Link 0, p | positive 2 | mRxLink0p | Module Re  | ceive Link 0, positive |

| 3      | mTxLink0n | Module Transmit Link 0, r | egative 4  | mRxLink0n | Module Re  | ceive Link 0, negative |

| 5      | mTxLink1p | Module Transmit Link 1, p | positive 6 | mRxLink1p | Module Re  | ceive Link 1, positive |

| 7      | mTxLink1n | Module Transmit Link 1, r | egative 8  | mRxLink1n | Module Re  | ceive Link 1, negative |

| 9      | Reserved  | Reserved                  | 10         | Reserved  | Reserved   |                        |

| 11     | Reserved  | Reserved                  | 12         | Reserved  | Reserved   |                        |

| 13     | Reserved  | Reserved                  | 14         | Reserved  | Reserved   |                        |

| 15     | Reserved  | Reserved                  | 16         | Reserved  | Reserved   |                        |

| 17     | Reserved  | Reserved                  | 18         | Reserved  | Reserved   |                        |

| 19     | Reserved  | Reserved                  | 20         | Reserved  | Reserved   |                        |

| 21     | Reserved  | Reserved                  | 22         | Reserved  | Reserved   |                        |

| 23     | Reserved  | Reserved                  | 24         | Reserved  | Reserved   |                        |

| 25     | Reserved  | Reserved                  | 26         | Reserved  | Reserved   |                        |

| 27     | Reserved  | Reserved                  | 28         | Reserved  | Reserved   |                        |

|        |           |                           |            |           |            |                        |

|        | Document  | No.                       | Revision   | Date      |            | Page 29 of 24          |

| D00    | 0002H-s   | pec.doc                   | 1.5        | 08/09/    | 06         | 1 age 27 01 24         |

#### 4.4.2.1.3. RSL Type A, Top, 8 Links, TIM

|        | -        |                          |        | -        |                           |

|--------|----------|--------------------------|--------|----------|---------------------------|

| Pin No | Pin Name | Signal Description       | Pin No | Pin Name | Signal Description        |

| 1      | RxLink0p | Receive Link 0, positive | 2      | TxLink0p | Transmit Link 0, positive |

| 3      | RxLink0n | Receive Link 0, negative | 4      | TxLink0n | Transmit Link 0, negative |

| 5      | RxLink1p | Receive Link 1, positive | 6      | TxLink1p | Transmit Link 1, positive |

| 7      | RxLink1n | Receive Link 1, negative | 8      | TxLink1n | Transmit Link 1, negative |

| 9      | RxLink2p | Receive Link 2, positive | 10     | TxLink2p | Transmit Link 2, positive |

| 11     | RxLink2n | Receive Link 2, negative | 12     | TxLink2n | Transmit Link 2, negative |

| 13     | RxLink3p | Receive Link 3, positive | 14     | TxLink3p | Transmit Link 3, positive |

| 15     | RxLink3n | Receive Link 3, negative | 16     | TxLink3n | Transmit Link 3, negative |

| 17     | Reserved | Reserved                 | 18     | Reserved | Reserved                  |

| 19     | Reserved | Reserved                 | 20     | Reserved | Reserved                  |

| 21     | Reserved | Reserved                 | 22     | Reserved | Reserved                  |

| 23     | Reserved | Reserved                 | 24     | Reserved | Reserved                  |

| 25     | Reserved | Reserved                 | 26     | Reserved | Reserved                  |

| 27     | Reserved | Reserved                 | 28     | Reserved | Reserved                  |

## 4.4.2.1.4. RSL Type B, Top, 8 Links, TIM

| Pin No | Pin Name | Signal Description        | Pin No | Pin Name | Signal De                | escription               |  |  |

|--------|----------|---------------------------|--------|----------|--------------------------|--------------------------|--|--|

| 1      | TxLink0p | Transmit Link 0, positive | 2      | RxLink0p | Receive L                | Link 0, positive         |  |  |

| 3      | TxLink0n | Transmit Link 0, negative | 4      | RxLink0n | Receive L                | Receive Link 0, negative |  |  |

| 5      | TxLink1p | Transmit Link 1, positive | 6      | RxLink1p | Receive L                | Receive Link 1, positive |  |  |

| 7      | TxLink1n | Transmit Link 1, negative | 8      | RxLink1n | Receive L                | link 1, negative         |  |  |

| 9      | TxLink2p | Transmit Link 2, positive | 10     | RxLink2p | Receive L                | Link 2, positive         |  |  |

| 11     | TxLink2n | Transmit Link 2, negative | 12     | RxLink2n | Receive L                | Receive Link 2, negative |  |  |

| 13     | TxLink3p | Transmit Link 3, positive | 14     | RxLink3p | Receive Link 3, positive |                          |  |  |

| 15     | TxLink3n | Transmit Link 3, negative | 16     | RxLink3n | Receive Link 3, negative |                          |  |  |

| 17     | Reserved | Reserved                  | 18     | Reserved | Reserved                 |                          |  |  |

| 19     | Reserved | Reserved                  | 20     | Reserved | Reserved                 |                          |  |  |

| 21     | Reserved | Reserved                  | 22     | Reserved | Reserved                 |                          |  |  |

| 23     | Reserved | Reserved                  | 24     | Reserved | Reserved                 |                          |  |  |

| 25     | Reserved | Reserved                  | 26     | Reserved | Reserved                 |                          |  |  |

| 27     | Reserved | Reserved                  | 28     | Reserved | Reserved                 |                          |  |  |

#### 4.4.2.1.5. RSL Type A, Top, 12 Links, TIM

| D: M   |           |                          | -      | -         | -                         |

|--------|-----------|--------------------------|--------|-----------|---------------------------|

| Pin No | Pin Name  | Signal Description       | Pin No | Pin Name  | Signal Description        |

| 1      | mRxLink0p | Receive Link 0, positive | 2      | mTxLink0p | Transmit Link 0, positive |

| 3      | mRxLink0n | Receive Link 0, negative | 4      | mTxLink0n | Transmit Link 0, negative |

| 5      | mRxLink1p | Receive Link 1, positive | 6      | mTxLink1p | Transmit Link 1, positive |

| 7      | mRxLink1n | Receive Link 1, negative | 8      | mTxLink1n | Transmit Link 1, negative |

| 9      | mRxLink2p | Receive Link 2, positive | 10     | mTxLink2p | Transmit Link 2, positive |

| 11     | mRxLink2n | Receive Link 2, negative | 12     | mTxLink2n | Transmit Link 2, negative |

| 13     | mRxLink3p | Receive Link 3, positive | 14     | mTxLink3p | Transmit Link 3, positive |

| 15     | mRxLink3n | Receive Link 3, negative | 16     | mTxLink3n | Transmit Link 3, negative |

| 17     | mRxLink4p | Receive Link 4, positive | 18     | mTxLink4p | Transmit Link 4, positive |

| 19     | mRxLink4n | Receive Link 4, negative | 20     | mTxLink4n | Transmit Link 4, negative |

| 21     | mRxLink5p | Receive Link 5, positive | 22     | mTxLink5p | Transmit Link 5, positive |

| 23     | mRxLink5n | Receive Link 5, negative | 24     | mTxLink5n | Transmit Link 5, negative |

| 25     | Reserved  | Reserved                 | 26     | Reserved  | Reserved                  |

| 27     | Reserved  | Reserved                 | 28     | Reserved  | Reserved                  |

#### 4.4.2.1.6.

## RSL Type B, Top, 12 Links, TIM

| Pin No | Pin Name  | Signal Description      |          | Pin No | Pin Name  | Signal I | Description              |

|--------|-----------|-------------------------|----------|--------|-----------|----------|--------------------------|

| 1      | mTxLink0p | Module Transmit Link 0, | positive | 2      | mRxLink0p | Module   | Receive Link 0, positive |

| 3      | mTxLink0n | Module Transmit Link 0, | negative | 4      | mRxLink0n | Module   | Receive Link 0, negative |

| 5      | mTxLink1p | Module Transmit Link 1, | positive | 6      | mRxLink1p | Module   | Receive Link 1, positive |

| 7      | mTxLink1n | Module Transmit Link 1, | negative | 8      | mRxLink1n | Module   | Receive Link 1, negative |

| 9      | mTxLink2p | Module Transmit Link 2, | positive | 10     | mRxLink2p | Module   | Receive Link 2, positive |

| 11     | mTxLink2n | Module Transmit Link 2, | negative | 12     | mRxLink2n | Module   | Receive Link 2, negative |

| 13     | mTxLink3p | Module Transmit Link 3, | positive | 14     | mRxLink3p | Module   | Receive Link 3, positive |

| 15     | mTxLink3n | Module Transmit Link 3, | negative | 16     | mRxLink3n | Module   | Receive Link 3, negative |

| 17     | mTxLink4p | Module Transmit Link 4, | positive | 18     | mRxLink4p | Module   | Receive Link 4, positive |

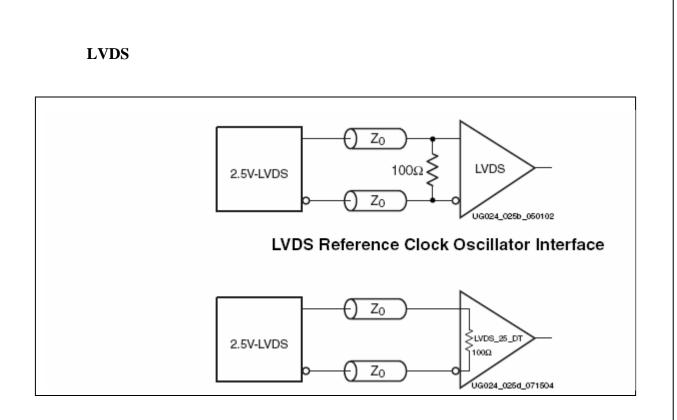

| 19     | mTxLink4n | Module Transmit Link 4, | negative | 20     | mRxLink4n | Module   | Receive Link 4, negative |