## USER GUIDE FOR

# **SMT417**

#### **Copyright © Sundance**

All rights reserved. No part of this document may be reproduced, translated, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording or otherwise, without prior written permission of the owner.

Note:

If this copy is no longer in use, return to sender.

| Document No.      | Revision | Date      | Page 1 of 72 |

|-------------------|----------|-----------|--------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 146010172    |

### APPROVAL PAGE

| Name              | Signature | Date |

|-------------------|-----------|------|

| Managing Director |           |      |

| Software Manager  |           |      |

| Design Engineer   |           |      |

|                   |           |      |

## AUTHOR/S

| Name | Signature | Date |

|------|-----------|------|

|      |           |      |

|      |           |      |

|      |           |      |

| Document No.      | Revision | Date      | Page 2 of 72 |

|-------------------|----------|-----------|--------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 |              |

## **DOCUMENT HISTORY**

| Date      | Changes Made                                                                                          | Issue | Initials |

|-----------|-------------------------------------------------------------------------------------------------------|-------|----------|

| 14-Feb-07 | Consolidated from Design Specification, work-in-<br>progress.                                         | 0.1   | BV       |

| 25-Feb-07 | Complete Draft Revision, for internal review                                                          | 0.2   | BV       |

| 27-Feb-07 | Repair issues in .pdf translation, fix some cross-<br>references, update ordering information section | 0.3   | BV       |

|           |                                                                                                       |       |          |

|           |                                                                                                       |       |          |

| Document No.      | Revision | Date      | Page 3 of 72  |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 4 5 6 7 7 2 |

## LIST OF ABBREVIATIONS

| Abbreviation   | Expla           | nation                                                      |                   |                  |  |

|----------------|-----------------|-------------------------------------------------------------|-------------------|------------------|--|

| ASIC           | Applica         | Application Specific Integrated Circuit                     |                   |                  |  |

| CMC            | Commo           | Common Mezzanine Card                                       |                   |                  |  |

| СР             | Commu           | Communications Port                                         |                   |                  |  |

| DSP            | Digital S       | Signal Processo                                             | or                |                  |  |

| FMS            | Trade r<br>Inc. | Trade name for a flat-ribbon cable family from JST Mfg Inc. |                   |                  |  |

| FPGA           | Field Pr        | ogrammable G                                                | ate Array         |                  |  |

| NA             | Not App         | licable                                                     |                   |                  |  |

| OTP            | One-Tir         | ne Programmal                                               | ble               |                  |  |

| PC             | Persona         | al Computer                                                 |                   |                  |  |

| РСВ            | Printed         | Circuit Board                                               |                   |                  |  |

| PCI            | Periphe         | Peripheral Component Interconnect                           |                   |                  |  |

| PMC            | PCI Me          | PCI Mezzanine Card                                          |                   |                  |  |

| PrPMC          | Process         | Processor PMC                                               |                   |                  |  |

| RF             | Radio F         | Radio Frequency                                             |                   |                  |  |

| RSL            | Rocketl         | RocketIO Serial Link                                        |                   |                  |  |

| SDB            | Sundan          | Sundance Digital Bus                                        |                   |                  |  |

| SDRAM          | Synchro         | Synchronous Dynamic Random Access Memory                    |                   |                  |  |

| SHB            | Sundan          | ce High-speed                                               | Bus               |                  |  |

| SMA            | Trade n         | ame for a threa                                             | ded RF co-axial   | connector family |  |

| SMT            | Sundan          | ce Multiproces                                              | sor Technology, I | LTD.             |  |

| TBD            | To Be D         | etermined                                                   |                   |                  |  |

| ТІ             | Texas li        | Texas Instruments                                           |                   |                  |  |

| XMC            | Switche         | Switched Mezzanine Card                                     |                   |                  |  |

| Document No.   |                 | Revision                                                    | Date              |                  |  |

| SMT417 User Gu | uide            | <b>0.3</b>                                                  | 27-Feb-07         | Page 4 of 72     |  |

## TABLE OF CONTENTS

| 1. INT | RODUCTION                 | ••••••   |                                         |               |

|--------|---------------------------|----------|-----------------------------------------|---------------|

| 1.1.   | Overview                  |          |                                         | 10            |

| 1.2.   | NOTATIONAL CONVENTIONS    |          |                                         |               |

| 1.3.   | INTENDED AUDIENCE         |          |                                         |               |

| 1.4.   | RELATED DOCUMENTS         |          |                                         |               |

|        |                           |          |                                         |               |

| 2. BLC | OCK DIAGRAM               | ••••••   | ••••••••••••••••••••••••••••••••••••••• |               |

| 2.1.   | Features                  |          |                                         |               |

| 3. ME  | CHANICAL INTERFACES       |          |                                         |               |

| 3.1.   | РМС                       |          |                                         | 13            |

| 3.1.   |                           |          |                                         |               |

| 3.1.   |                           |          |                                         |               |

| 3.1.   |                           |          |                                         |               |

| 3.1.4  |                           |          |                                         |               |

| 3.1.   | •                         |          |                                         |               |

| 3.1.   | 8                         |          |                                         |               |

| 3.1.   | 0                         |          |                                         |               |

| 3.1.   |                           |          |                                         |               |

| 3.1.   |                           |          |                                         |               |

| 3.2.   | XMC                       |          |                                         |               |

| 3.2.   |                           |          |                                         |               |

| 3.2.   |                           |          |                                         |               |

| 3.2.   | 1                         |          |                                         |               |

| 3.2.4  |                           |          |                                         |               |

| 3.2.   |                           |          |                                         |               |

| 3.2.   |                           |          |                                         |               |

| 3.3.   | FMS                       |          |                                         |               |

| 3.4.   | SHB                       |          |                                         |               |

| 3.5.   | RSL                       |          |                                         |               |

| 3.6.   | GRF                       |          |                                         |               |

| 3.0.   | JTAG                      |          |                                         |               |

| 3.8.   | GPIO                      |          |                                         |               |

| 3.9.   | EXTERNAL POWER            |          |                                         |               |

|        |                           |          |                                         |               |

| 4. DEV | VICES                     |          |                                         |               |

| 4.1.   | QL5064 PCI Bridge         |          |                                         |               |

| 4.2.   | CPLD                      |          |                                         |               |

| 4.3.   | FPGA                      |          |                                         |               |

| 4.4.   | DSP                       |          |                                         |               |

| 4.4.   | 1. EMIF Interface to FPGA |          |                                         |               |

| 4.4.2  | 2. FLASH                  |          |                                         |               |

| 4.4    | 3. HPI                    | •••••    |                                         |               |

| 4.4.4  | 4. McBSP                  |          |                                         |               |

| 4.4    | 5. PCI Interface          | •••••    |                                         |               |

| 4.4.   | 6. SDRAM                  |          |                                         |               |

| 4.4.   | 7. UTOPIA                 |          |                                         |               |

| 5. OPI | ERATION                   |          |                                         |               |

| 5 1    | OI 5064 PRIDCE SETUR      |          |                                         | 22            |

| 5.1.   | QL5064 BRIDGE SETUP       |          |                                         |               |

| 5.1.   |                           |          |                                         |               |

| 5.1.2  |                           |          |                                         |               |

| 5.1    |                           |          |                                         |               |

| 5.2.   | CPLD OPERATION            |          |                                         |               |

|        |                           |          |                                         |               |

|        | Document No.              | Revision | Date                                    | Page 5 of 72  |

| G      | SMT417 User Guide         | 0.3      | 27-Feb-07                               | 1 age 5 01 72 |

|        | mitti osci Guiuc          | 0.5      |                                         |               |

| 5.2.1          | CPLD MAGIC Register                   |          |           |              |

|----------------|---------------------------------------|----------|-----------|--------------|

| 5.3.           | FPGA CONFIGURATION                    |          |           |              |

| 5.3.1          |                                       |          |           |              |

| 5.3.2          |                                       |          |           |              |

| 5.3.3          | DSP via CPLD under Bootload           |          |           |              |

| 5.3.4          | PCI via CPLD                          |          |           |              |

| 5.4.           | FPGA I/O INTERFACES                   |          |           |              |

| 5.4.1          | Comports                              |          |           |              |

| 5.4.2          | P. PCI                                |          |           |              |

| 5.4.3          |                                       |          |           |              |

| 5.4.4          |                                       |          |           |              |

| 5.4.5          | · · · · · · · · · · · · · · · · · · · |          |           |              |

| 5.4.6          |                                       |          |           |              |

| 5.5.           | DSP                                   |          |           |              |

| 5.5.1          |                                       |          |           |              |

| 5.5.2          |                                       |          |           |              |

| 5.5.3<br>5.5.4 |                                       |          |           |              |

| 5.5.5          | 8                                     |          |           |              |

| 5.5.6          |                                       |          |           |              |

| 5.5.7          |                                       |          |           |              |

| 5.5.8          |                                       |          |           |              |

| 5.5.9          |                                       |          |           |              |

| 5.5.1          |                                       |          |           |              |

| 5.6.           | CLOCK SOURCES                         |          |           |              |

| 5.7.           | Power Supplies                        |          |           |              |

| 5.8.           | RESET HIERARCHY                       |          |           |              |

| 6. APP         | LICATION DEVELOPMENT                  |          |           | 13           |

|                |                                       |          |           |              |

| 6.1.           | SMT6400                               |          |           |              |

| 6.2.           | 3L DIAMOND                            |          |           |              |

| 6.3.           | SMT6045                               |          |           |              |

| 6.4.           | PARS                                  |          |           |              |

| 7. CON         | NTROL REGISTER DESCRIPTIONS           | 5        | •••••••   |              |

| 7.1.           | QL5064 Registers                      |          |           |              |

| 7.1.1          | -                                     |          |           |              |

| 7.1.2          | Revision ID Register                  |          |           |              |

| 7.1.3          | 8                                     |          |           |              |

| 7.1.4          |                                       |          |           |              |

| 7.1.5          |                                       |          |           |              |

| 7.2.           | CPLD REGISTERS                        |          |           |              |

| 7.2.1          | . CPLD VERSION Register               |          |           |              |

| 7.2.2          | C. CPLD SMCTL Register                |          |           |              |

| 7.2.3          | - 0                                   |          |           |              |

| 7.2.4          | 8                                     |          |           |              |

| 7.2.5          |                                       |          |           |              |

| 7.2.6          | 8                                     |          |           |              |

| 7.3.           | FPGA I/O INTERFACE REGISTERS          |          |           |              |

| 7.3.1          | 0                                     |          |           |              |

| 7.3.2          | 50 0                                  |          |           |              |

| 7.3.4          | 0                                     |          |           |              |

| 7.3.4          | 8                                     |          |           |              |

|                |                                       |          |           |              |

| 8. FOC         | DTPRINT                               | ••••••   | ••••••    |              |

| 8.1.           | Тор                                   |          |           |              |

| 8.2.           | Воттом                                |          |           |              |

| 8.3.           | Edge View                             |          |           |              |

| 8.4.           | MECHANICAL LAYOUT DIAGRAMS            |          |           |              |

|                | Dogument No.                          | Davisian | Data      |              |

|                | Document No.                          | Revision | Date      | Page 6 of 72 |

| S              | MT417 User Guide                      | 0.3      | 27-Feb-07 |              |

| 9. PINOUT                            |                                  |

|--------------------------------------|----------------------------------|

| 9.1. PCI                             |                                  |

| 9.1.1. PMC P11 Connector             |                                  |

| 9.1.2. PMC P12 Connector             |                                  |

| 9.1.3. PMC P13 Connector             |                                  |

| 9.1.4. PMC P14 Connector             |                                  |

| 9.2. SHB                             | • • •                            |

| 9.2.1. SHB JA3 Connector             |                                  |

| 9.2.2. SHB JA4 Connector             |                                  |

| 9.3. JTAG                            |                                  |

| 9.3.1. J2 Header                     |                                  |

| 9.4. XMC                             |                                  |

| 9.4.1. J5 (P15) Header               |                                  |

| 9.4.2. PCIe Support                  |                                  |

| 9.5. FMS                             |                                  |

| 9.5.1. J3 Pin Allocation             |                                  |

| 9.5.2. J4 Pin Allocation<br>9.6. RSL |                                  |

| 9.6. RSL                             |                                  |

| 9.0.1. JAO Pin Auocanon<br>9.7. GRF  |                                  |

| 9.7.1. JA5 Pin Allocation            |                                  |

| 9.8. LED                             |                                  |

| 9.9. GPIO                            |                                  |

| 9.9.1. JA2 Pin Allocation            |                                  |

| 9.10. External Power                 |                                  |

| 9.10.1. JA1 Pin Allocation           | •••••••••••••••••••••••••••••••• |

|                                      |                                  |

| 10. OPERATING CONDITIONS             |                                  |

| 10.1. Power Estimate                 |                                  |

| 10.2. Power Requirements             |                                  |

| 10.3. THERMAL                        |                                  |

| 10.4. SAFETY                         |                                  |

| 10.5. EMC                            |                                  |

| 11. DATASHEETS                       |                                  |

| 12. ORDERING INFORMATION             |                                  |

| 12.1. Examples                       | 77                               |

|                                      |                                  |

|                                      |                                  |

|                                      |                                  |

| Document No.      | Revision | Date      | Page 7 of 72  |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 age 7 01 72 |

## **TABLE OF FIGURES and TABLES**

| Figure 1 - Block diagram of the SMT417                      |          |           |               |  |

|-------------------------------------------------------------|----------|-----------|---------------|--|

| Figure 2 - Single-size PMC card (from IEEE 1386-2001)       |          |           |               |  |

| Figure 3 - Single-size XMC card (from ANSI/V                | /ITA 42) |           | 14            |  |

| Figure 4 - XMC Connector Outline                            |          |           |               |  |

| Figure 5 - FMS Connector Outline                            |          |           | 16            |  |

| Figure 6 - SHB Connector Outline                            |          |           |               |  |

| Figure 7 - RSL QTE-014-xx-DP Type Connector                 |          |           |               |  |

| Figure 8 - GRF1-J Connector Outline                         |          |           |               |  |

| Figure 9 - HW-AFX-SMA-SATA                                  |          |           |               |  |

| Figure 10 - HW-AFX-SMA-SFP                                  |          |           |               |  |

| Figure 11 - Outboard JTAG adapter for SMT4                  | 17       |           | 19            |  |

| Figure 12 - Block diagram of SMT417 FPGA (                  | (v0.1)   |           | 21            |  |

| Figure 13 - Xilinx FPGA JTAG Port on JTAG                   | Adapter  |           | 27            |  |

| Figure 14 - Devices on the FPGA JTAG Chain.                 |          |           | 27            |  |

| Figure 15 - Comport Links to DSPs                           |          |           |               |  |

| Figure 16 - SHB Links to DSPs                               |          |           |               |  |

| Figure 17 - DSP TCLKx Routing                               |          |           |               |  |

| Figure 18 - XDS510 JTAG Port on JTAG Adapter                |          |           |               |  |

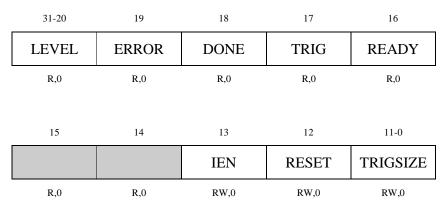

| Figure 19 - SMT417 v2 PCB Top Layout (Side 1)               |          |           |               |  |

| Figure 20 - SMT417 v2 PCB Bottom Layout (Side 2 X-RAY VIEW) |          |           |               |  |

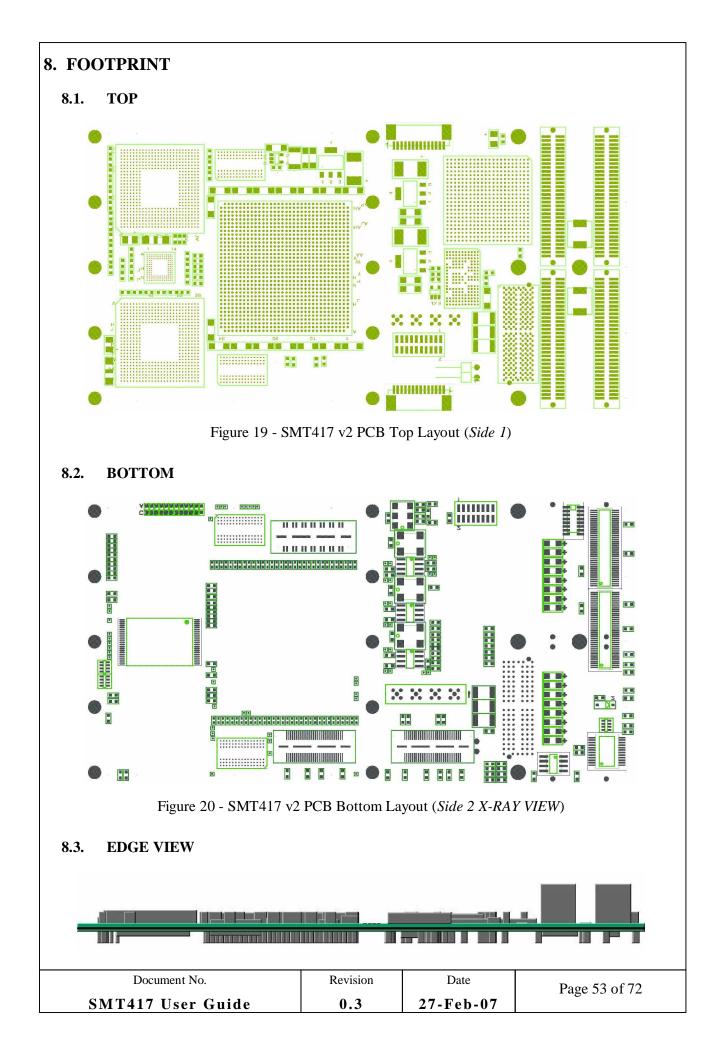

| Figure 21 - Side 1 Mechanical Diagram                       |          |           |               |  |

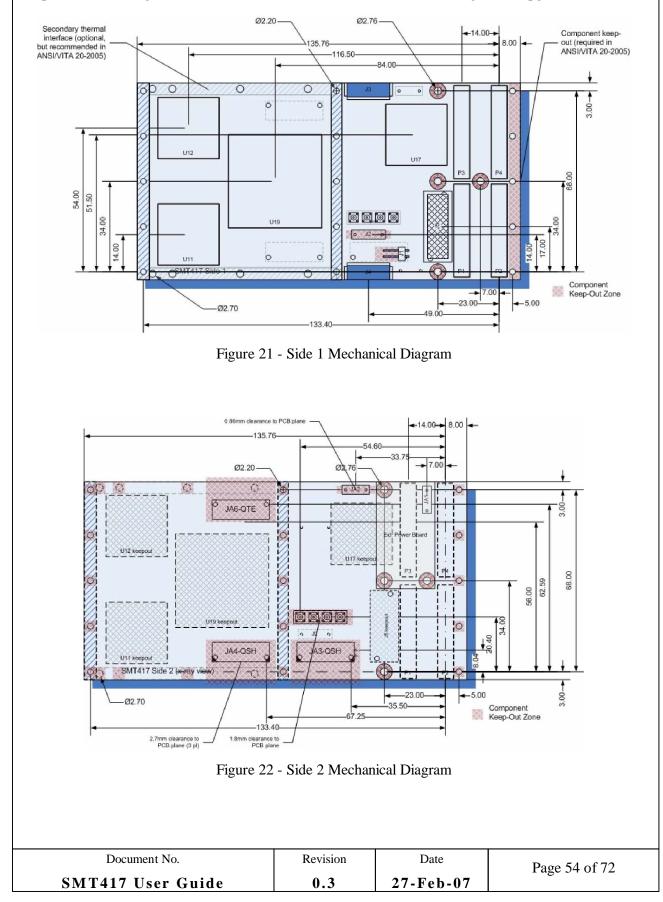

| Figure 22 - Side 2 Mechanical Diagram                       |          |           | 54            |  |

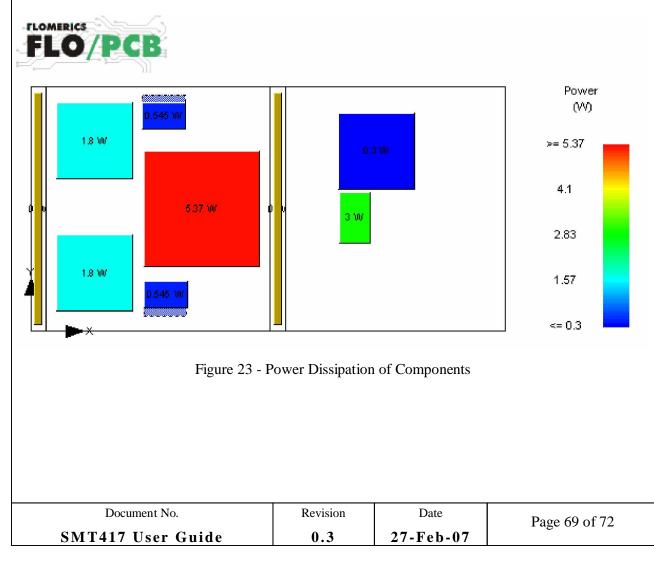

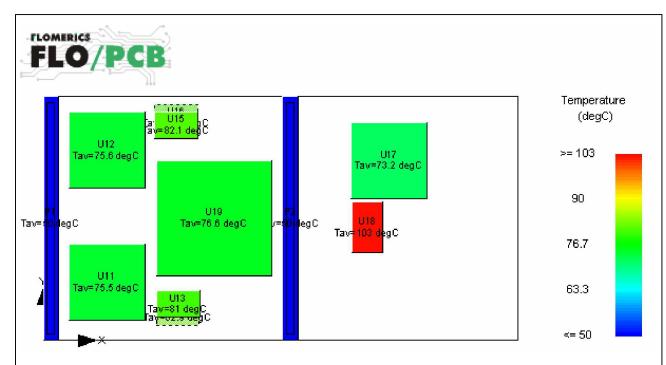

| Figure 23 - Power Dissipation of Components                 |          |           | 69            |  |

| Figure 24 - Thermal Solution for SMT417                     |          |           | 70            |  |

|                                                             |          |           |               |  |

| Table 1 - Base Address Region Setup Paramete                | ers      |           |               |  |

| Table 2 – Base Address Region Descriptions                  |          |           | 24            |  |

| Table 3 - CPLD Register Pages                               |          |           |               |  |

| Table 4 - MGT Cross-Reference for SMT417 H                  | PCB V2   |           |               |  |

| Table 5 - MGT Allocation vs. FPGA Size    33                |          |           |               |  |

| Table 6 - MGT Clock Sources on SMT417                       |          |           |               |  |

| Table 7 - FPGA Interrupt Lines                              |          |           |               |  |

| Table 8 - CPLD Register Addresses in DSPA Memory            |          |           |               |  |

| Table 9 - DSP EMIF Register Setup Values                    |          |           |               |  |

| Table 10 - DSP NAND FLASH Register Assignments              |          |           |               |  |

| Table 11 - SMT417 Default FLASH Organizat                   | ion      |           |               |  |

| Document No.                                                | Revision | Date      | Page 8 of 72  |  |

| SMT417 User Guide                                           | 0.3      | 27-Feb-07 | 1 450 0 01 72 |  |

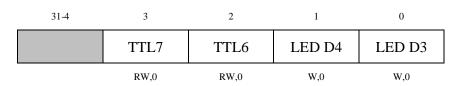

| Table 12 - Timer Control Register            |              |           |              |

|----------------------------------------------|--------------|-----------|--------------|

| Table 13 - LED and GPIO Register for DSPA    | (0x01B00008) |           | 40           |

| Table 14 - LED and GPIO Register for DSPB    | (0x01B00008) |           | 40           |

| Table 15 - QL5064 Register Offsets in BAR0.  |              |           | 44           |

| Table 16 - QL5064 GPIO Register Bits         |              |           |              |

| Table 17 - QL5064 GPIO Device Routing        |              |           |              |

| Table 18 - QL5064 Local Bus Control Register | r Bits       |           | 46           |

| Table 19 - CPLD Register Pages               |              |           | 47           |

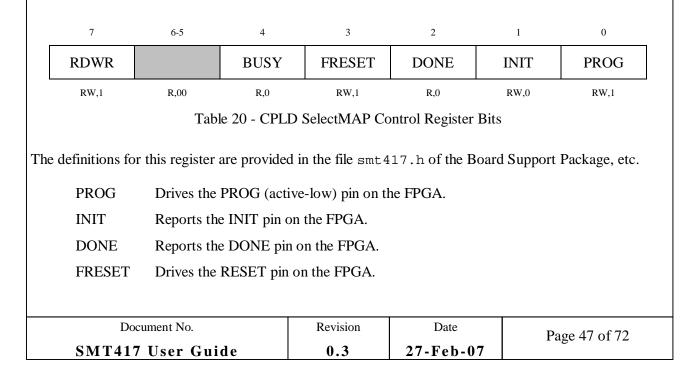

| Table 20 - CPLD SelectMAP Control Register   | Bits         |           | 47           |

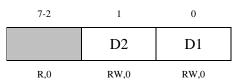

| Table 21 - CPLD DSP JTAG Control Register    | Bits         |           | 48           |

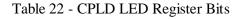

| Table 22 - CPLD LED Register Bits            |              |           |              |

| Table 23 - CPLD DSP JTAG Control Register    | Bits         |           |              |

| Table 24 - FPGA Register Offsets in BAR1     |              |           |              |

| Table 25 – FPGA Port Configuration Register  | Bits         |           | 51           |

| Table 26 – FPGA Global Control Register Bits |              |           | 51           |

| Table 27 – FPGA Link Port Control/Status Reg | gister Bits  |           |              |

| Table 28 - P11 Pin Assignments               |              |           | 55           |

| Table 29 - P12 Pin Assignments               |              |           |              |

| Table 30 - P13 Pin Assignments               |              |           | 57           |

| Table 31 - P14 Pin Assignments               |              |           |              |

| Table 32 - General SHB Pin Allocation        |              |           |              |

| Table 33 - JA3 Pin Assignments               |              |           | 60           |

| Table 34 - JA4 Pin Assignments               |              |           | 61           |

| Table 35 - J2 Header Pinout                  |              |           |              |

| Table 36 - J5 (P15) Pin Allocation           |              |           | 63           |

| Table 37 - P15 Signals for PCIe Support      |              |           | 63           |

| Table 38 – General FMS Pin Allocation        |              |           | 64           |

| Table 39 - J3 Pin Allocation                 |              |           | 64           |

| Table 40 – J4 Pin Allocation                 |              |           | 65           |

| Table 41 - JA6 Pin Allocation                |              |           | 65           |

| Table 42 - JA5 Pin Allocation (SMT417 PCB    | V2)          |           | 66           |

| Table 43 - LED Signal Allocation             |              |           | 66           |

| Table 44 - JA2 Pin Allocation                |              |           | 67           |

| Table 45 – JA1 Pin Allocation                |              |           | 67           |

| Table 46 - Full Power Dissipation Estimate   |              |           |              |

| Table 47 - Power Budget based on Supply      |              |           | 69           |

|                                              |              |           |              |

|                                              |              |           |              |

| Document No.                                 | Revision     | Date      | Page 9 of 72 |

| SMT417 User Guide                            | 0.3          | 27-Feb-07 | 6            |

#### **1. INTRODUCTION**

#### 1.1. OVERVIEW

This document describes the features and operations of a PMC module with two fixed-point DSPs, one large FPGA, and several external I/O interfaces.

#### **1.2. NOTATIONAL CONVENTIONS**

#### DSP

The term DSP will be used throughout this document in place of TMS320C6416T.

#### **Register Descriptions**

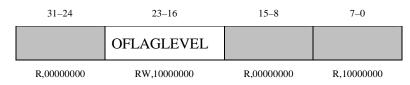

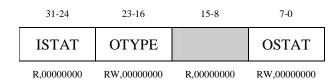

The format of registers is described using diagrams of the following form:

The digits at the top of the diagram indicate bit positions within the register and the central section names bits or bit fields. The bottom row describes what may be done to the field and its value after reset. Shaded fields are reserved and should only ever be written with zeroes.

| R    | Readable by the CPU               |

|------|-----------------------------------|

| W    | Writeable by the CPU              |

| RW   | Readable and writeable by the CPU |

| W1TC | Write 1 to Clear                  |

|      |                                   |

Binary digits indicate the value of the field after reset

#### **1.3. INTENDED AUDIENCE**

This document describes all interfaces available based on the design specification of the SMT417. SMT417 boards with the following PCB versions have the following restrictions:

| V1 Red Solder Mask,  | Merix Label N      | N/A    | No PMC/PCI, No XMC (stand-alone use only) |

|----------------------|--------------------|--------|-------------------------------------------|

| V2 Green Solder Mask | k, Sierra Label 02 | xB0102 | No XMC, CPLD bit swizzle required         |

| Document No.      | Revision | Date      | Page 10 of 72   |

|-------------------|----------|-----------|-----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 4 50 10 01 72 |

#### **1.4. RELATED DOCUMENTS**

[1] PCI Mezzanine Card (*PMC*) Specification – IEEE 1386-2001.

http://standards.ieee.org/reading/ieee/std/busarch/1386-2001\_and\_1386.1-2001.pdf

[2] Sundance High-speed Bus (SHB) Specification – Sundance.

http://sundance.com/docs/SHB% 20Technical% 20Specification.pdf

[3] External Interface User Manual – Sundance.

http://sundance.com/docs/Firmware.pdf

[4] Rocket Serial Link (*RSL*) Specification – Sundance.

http://www.sundance.com/docs/Specification\_RSL.pdf

[5] Processor PMC (PrPMC) Specification – VITA 32.

http://www.vita.com/specifications.html

[6] (FMS) Specification - Sundance

ftp://ftp2.sundance.com/Pub/documentation/pdf-files/comm-port.pdf

[7] Switched Mezzanine Card (XMC) Specification- VITA 42

http://www.vita.com/specifications.html

| Document No.      | Revision | Date      | Page 11 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1450 11 01 72 |

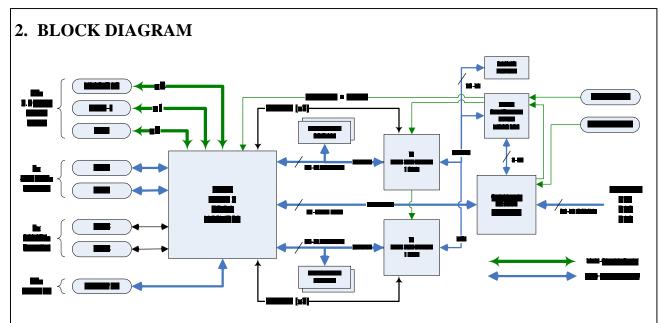

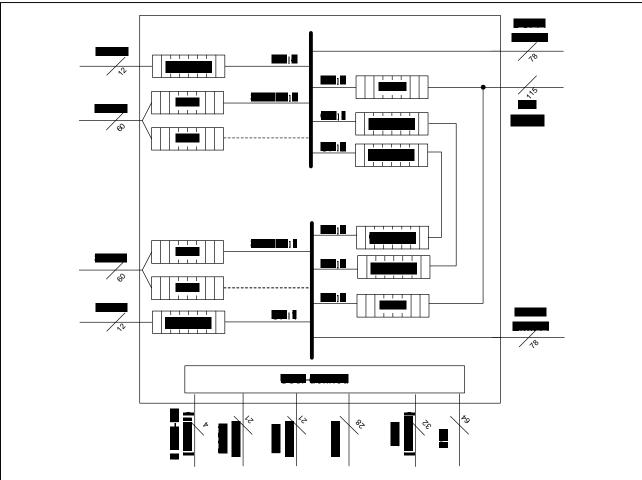

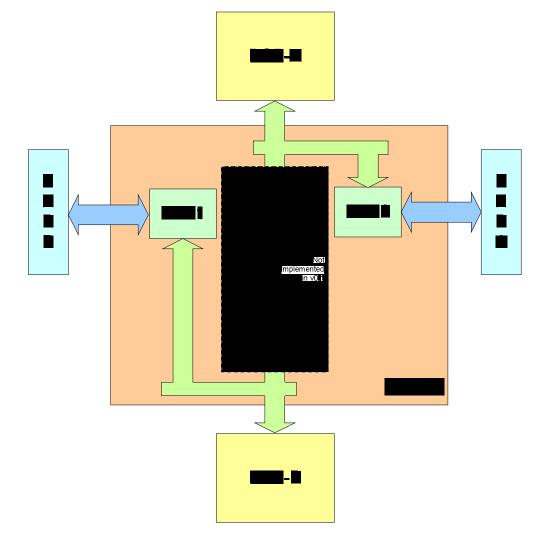

Figure 1 - Block diagram of the SMT417.

The SMT417 enables hybrid DSP/FPGA computation on digital data acquired from PCI, SHB or RSL interfaces while conforming to a single-sized PMC form factor.

#### 2.1. FEATURES

The main features of the *SMT417* are listed below:

- § Two <u>TI 6416T</u> DSPs with independent SDRAM

- § Xilinx Virtex II Pro (FF1152 package)

- § Provision for data processing in FPGA

- § One XMC connector with 8 RSL data links

- § Two FMS connectors

- § Standard single-size PMC module

- § 66MHz 64-bit PCI interface with over 500MB/s data rate

- § Standard Sundance software interface

Additional features meeting ANSI/VITA 32 (PrPMC) spec for tall modules:

- § Two <u>SHB</u> *AND* one <u>RSL</u> (7x bidirectional RocketIO) interface for easy interconnection to Sundance products.

- § One (1x bidirectional RocketIO) to a Samtec <u>GRF1-J</u> connector for interfacing to Xilinx RocketIO connectivity boards and other custom multi-gigabit serial interface hardware.

| Document No.      | Revision | Date      | $P_{\text{area}} 12 \text{ of } 72$ |

|-------------------|----------|-----------|-------------------------------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | Page 12 of 72                       |

#### **3. MECHANICAL INTERFACES**

#### **3.1. PMC**

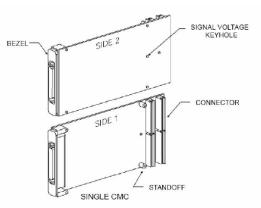

PMC is a variant of CMC that uses PCI to communicate over the backplane. The IEEE CMC standard describes both single- and double-size mezzanine cards. The SMT417 is a single-size card.

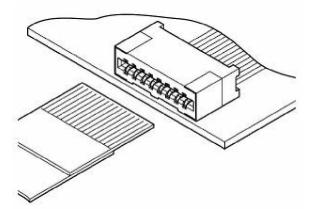

Figure 2 - Single-size PMC card (from IEEE *1386-2001*)

Dimensions of the single-size CMC are 74.0mm wide by 149.0mm deep. Note that the SMT417 does not provide any front panel connectors or ports, as per the ANSI/VITA 20 (conduction cooled specification).

#### 3.1.1. Voltage keying

The QuickLogic QL5064 bridge is both 3.3V and 5V compliant. Both keying holes are provided. *Note that the SMT417 requires both 3.3V and 5V power to function.*

#### 3.1.2. Connectors

P11 through P13 are required for 64-bit PCI connectivity. Connector P14 is provided for 64 user-defined I/O.

#### **3.1.3.** Component Height

Heights of components on PMC Side 1 (see Figure 2) are limited to 4.7mm except in the I/O Area (where they may extend to the host module surface). Components on PMC Side 2 are limited to 3.5mm minus PCB thickness, or about 2.0mm (assuming 1.5mm PCB thickness).

The SMT417 has build options which place certain external I/O connectors onto Side 2. When ordered in this way, the SMT417 conforms to ANSI/VITA 32 (PrPMC), which allows 10mm to 20mm of height above the PCB for components on Side 2.

#### **3.1.4.** Power Consumption

Based on the IEEE 1386-2001 specification, the total consumption for Side 1 and Side 2 of the module shall not exceed 7.5W. Depending on the operating frequency and user-defined FPGA designs implemented, the SMT417 is easily capable of exceeding the recommended power dissipation limits. Careful planning at both the software and firmware levels is required when integrating the SMT417 into end-user systems.

| Document No.      | Revision | Date      | Page 13 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 |               |

#### 3.1.5. Cooling

The SMT417 is designed to be used with conduction-cooled PMC carriers and systems. The specifications governing this are defined by ANSI/VITA 20-2001. The specification defines certain areas on the PMC board to be reserved free of components, to contain significant amounts of metal for thermal conductivity and to provide numerous through-hole terminals for attaching thermal and stiffening components.

#### 3.1.6. Grounding

Per section 4.14 of IEEE 1386-2001.

#### **3.1.7. PMC JTAG**

The ANSI/VITA 42 specification governs how the JTAG signals are to be treated. The SMT417 does not attach any devices to the PMC JTAG pins, but routes TDI->TDO to maintain integrity of any chains on the carrier boards. All manufacturing tests of the SMT417 are performed using the dedicated JTAG header.

#### 3.1.8. PMC P14 Connector

The SMT417 provides a P14 connector for user defined I/O. All signals are brought to the FPGA to allow customer defined functionality to be implemented. The signals are +5V tolerant<sup>1</sup> by way of a pair of QS34X245Q3 'quick switches'.

#### 3.1.9. Compliance

The SMT417 conforms to EN61000-4-2 for EMC and ANSI/VITA 47-2005 for other mechanical and environmental requirements.

#### 3.2. XMC

XMC is an extension of CMC that uses implements multi-gigabit switched serial connections to the backplane. The ANSI/VITA 42 standard describes both single- and double-size mezzanine cards. The SMT417 is a single-size card implementing an 8-lane interface to the XMC connector.

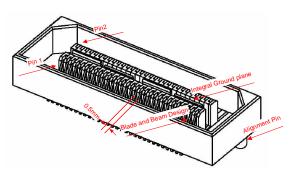

Figure 3 - Single-size XMC card (from ANSI/VITA 42)

<sup>1</sup> The XC2VP50 FPGA does *not* have 5V tolerant I/O.

| Document No.      | Revision | Date      | Page 14 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 |               |

#### 3.2.1. ANSI/VITA 42.2 Serial RapidIO

ANSI/VITA 42.2 defines requirements and considerations for implementing Serial RapidIO over XMC to switched serial carriers. The SMT417 *is* electrically compatible with this standard. Two x4 links are available to the connector. A user will have the option of introducing a Serial RapidIO core to the FPGA on the SMT417 to allow it to interact with the fabric.

#### 3.2.2. ANSI/VITA 42.3 PCI Express

ANSI/VITA 42.3 defines requirements and considerations for implementing PCI Express over XMC to switched serial carriers. The SMT417  $is^2$  electrically compatible with this standard. One x8 link is available to the connector. A user will have the option of introducing a PCI Express core to the FPGA on the SMT417 to allow it to interact with the fabric.

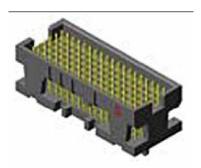

#### 3.2.3. XMC Connector

The SMT417 implements a primary (P15) interface only. The 8 lanes are routed as differential pairs directly to the FPGA according to ECMA-342, "Partition VI - Physical Layer 1x/4x LP-Serial Specification". AC coupling is used on the receivers.

Figure 4 - XMC Connector Outline

#### **3.2.4. XMC JTAG**

The ANSI/VITA 42 specification governs how the JTAG signals are to be treated. The SMT417 does not attach any devices to the XMC JTAG pins, but routes TDI->TDO to maintain integrity of any chains on the carrier boards. All manufacturing tests of the SMT417 are performed using the dedicated JTAG header.

#### 3.2.5. XMC IPMI

The SMT417 conforms to ANSI/VITA 42 Sec 5.4 by providing an I2C interface from the XMC connector to the CPLD. Contact Sundance DSP for details on CPLD revisions needed to support this part of the specification.

http://www.xilinx.com/xlnx/xil\_ans\_display.jsp?BV\_UseBVCookie=yes&getPagePath=18329

The SMT417 design uses a single ICS874005 to perform the 100MHz -> 125MHz conversion:

http://www.icst.com/icscs/SiteSearch.aspx?q=ICS874005

| Document No.      | Revision | Date      | Page 15 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 420 13 01 72 |

<sup>&</sup>lt;sup>2</sup> The PCIe reference clock (REFCLK+/-) needs to be handled by a PLL:

#### 3.2.6. XMC VPWR

The ANSI/VITA 42 specification allows "Variable Power" to be applied at either +5V or +12V. The SMT417 is designed to accommodate one or the other according to build option. It is important to know whether your carrier board is configured for +5V VPWR or +12V VPWR and order the SMT417 appropriately.

Do not connect an SMT417 incorrectly!

#### 3.3. FMS

2 FMS connectors are provided on side 1 of the board. They are present on all build options.

Figure 5 - FMS Connector Outline

An FMS connector provides 14 signal lines that typically implement an 8-bit digital link port according to the TI C40 comport link specification. The signal lines are connected directly to the FPGA, and can support typical signalling rates of 20MHz per bit. These are provided to make simple integration with other boards to create multiprocessor systems. The default FPGA design implements the Sundance Digital Link<sup>3</sup> (SDL/Comport) interface to allow simple connectivity between other Sundance carrier boards such as the SMT300 (Q) and SMT310 (Q).

#### 3.4. SHB

The SMT417 can (optionally) include two Sundance High-speed Bus (SHB) interfaces, both on side two of the board. These are only populated if option 'E' is ordered.

<sup>&</sup>lt;sup>3</sup> <u>http://www.sundance.com/docs/SDL%20Technical%20Specification.pdf</u>

| Document No.      | Revision | Date      | Page 16 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1080 10 01 /2 |

Figure 6 - SHB Connector Outline

An SHB connector provides 60 signal lines that typically implement the 16-bit Sundance Digital Bus (SDB) or 32-bit Sundance High Speed Bus<sup>4</sup> (SHB) interface. The signal lines are connected directly to the FPGA, and can support signalling rates of at least 133MHz per bit.

Please note that if the SHB connectors are mounted (a build-time option), the module becomes governed by the ANSI/VITA 32 specification (PrPMC). This may preclude spacing the PMC carrier boards in adjacent slots. Interfacing between SHB connectors on boards can be done by using Sundance SMT511-320, SMT512-DD, or SMT512-DA cables. See Section 9.2. below for additional details on cabling options.

#### 3.5. RSL

The SMT417 can (optionally) include one Sundance RocketIO Serial Link (RSL) interface, present on side two of the board. These are only populated if option 'E' is ordered. This interface is connected directly to the MGT pairs of the FPGA and can support clock rates of up to 3.125GHz, depending on the speed grade of the FPGA that is ordered and the frequency of the reference clock oscillator fitted.

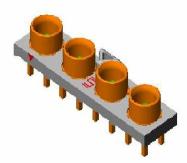

Figure 7 - RSL QTE-014-xx-DP Type Connector

The SMT417 implements a 7-lane interface to a "Type A" RSL connector. Interfacing to Sundance TIM modules can be accomplished using SMT522-RSL10 cables<sup>5</sup>. Interfacing to another SMT417 requires an SMT522-320-HE or SMT522-320-EH cable<sup>6</sup>. See Section 9.6. below for details on cabling options.

#### 3.6. GRF

The SMT417 can (optionally) include one GRF1-J connector, present on side two of the board and populated with the 'E' option of the board. The connector provides 4 separate coaxial connector ports in

http://www.precisionint.com/tdibrsb/images/drawings/D023850NNNLLLEH00.pdf

| Document No.      | Revision | Date      | Page 17 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1450 17 01 72 |

<sup>&</sup>lt;sup>4</sup> <u>ftp://ftp2.sundance.com/Pub/documentation/pdf-files/SHB\_Technical\_Specification.pdf</u>

<sup>&</sup>lt;sup>5</sup> <u>http://www.sundance.com/web/files/productpage.asp?STRFilter=SMT522-RSL10</u>

<sup>&</sup>lt;sup>6</sup> http://www.precisionint.com/tdibrsb/images/drawings/D023850NNNLLLHE00.pdf

a very small space. Each coaxial port is connected to one MGT signal, thus with 4 ports, a single lane (bidirectional) interface is exposed.

Figure 8 - GRF1-J Connector Outline

The GRF connector is provided to allow customers to convert MGT signals to individual coaxial cables, with standard ends, such as SMA, using the mating GRF1-C from Samtec.

Figure 9 - HW-AFX-SMA-SATA

Figure 10 - HW-AFX-SMA-SFP

These and many other conversion modules can be used to enable the SMT417 to connect its MGT signals to a wide variety of interfaces. See Section 9.7. below for details on cabling options.

#### **3.7. JTAG**

The SMT417 provides in-circuit debugging of its programmable DSP and FPGA devices. The JTAG chains for DSP and FPGA are electrically separate, allowing them to be used independently and concurrently. A small 20-pin header (J2) is fitted on side 1 under all build options. The header allows a ribbon cable to connect to an outboard JTAG adapter board.

| Document No.      | Revision | Date      | Page 18 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | r age 18 01 72 |

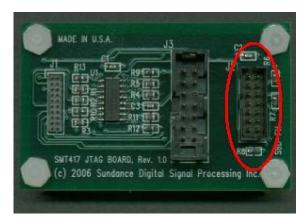

Figure 11 - Outboard JTAG adapter for SMT417

The JTAG adapter for the SMT417 provides a standard XDS510 JTAG port for the DSP. The adapter board also provides a standard Xilinx Parallel Cable IV port for the FPGA.

#### **3.8. GPIO**

The SMT417 can (optionally) be configured to provide several general purpose I/O (GPIO) signals, populated with the 'E' build option. 8 signal pins, two +3.3V pins and 6 GND pins are provided on a 16-pin header. See Section 9.9. below for pinout details.

#### **3.9. EXTERNAL POWER**

The SMT417 can (optionally) be configured to operate outside of a PMC/XMC system. In order to do this, +5V and +3.3V power needs to be supplied to the SMT417. A connector is populated for this purpose, once again under the 'E' build option.

Sundance provides a small outboard adapter board with power supply that is fitted onto this connector to provide a single (+5V) external supply input using a standard Molex (PC disk drive) connector. See section 9.10. below for pinout details.

| Document No.      | Revision | Date      | Page 19 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 450 19 01 72 |

#### 4. DEVICES

#### 4.1. QL5064 PCI BRIDGE

The PCI interface is implemented by a QuickLogic QL5064<sup>7</sup>. The QL5064 includes a hard PCI ASIC as well as an OTP fabric. In the SMT417, the QL5064 is preconfigured with the "Companion Design" logic from QuickLogic. This device bridges the PCI bus to a "Local Bus" on the SMT417 that connects the QL5064 with the XC2VP50 FPGA and the XC2C256 CPLD.

The QL5064 implements a 64-bit bus interface to the FPGA and allows the FPGA full access to the DMA controllers, the single-access PCI controller, and the target read/write buffers.

The QL5064 implements a simple 8-bit bus interface to the CPLD which has the ability to configure the FPGA, control system reset state and access the DSP JTAG chain.

In either case, the FPGA and CPLD devices appear in a PCI HOST memory mapped region, and control operations are effected by reading/modifying/writing registers on either the QL5064, CPLD or the FPGA.

#### 4.2. CPLD

The CPLD on the SMT417 implements system reset control, FPGA SelectMAP programming and DSP JTAG interface functions. The CPLD is addressable by the PCI as well as by DSPA. The PCI side provides full access to the CPLD registers, while the DSP side provides access to a sub-set of them.

From the PCI side, the board can be reset as a whole, or just the FPGA or the DSPs can be reset.

Both sides can access the FPGA (re-)configuration interface allowing either the DSP or the PCI to update the FPGA design. As the FPGA is separated from the PCI via the (unchanging) QL5064 bridge, a variety of FPGA interfaces can be presented to the PCI bus without restarting the driver or the HOST operating system.

The PCI side also enables access to the DSP JTAG chain. If suitable host-side support is provided, this allows users to control the DSP via JTAG for debugging without the need of an external emulator<sup>8</sup>.

#### **4.3. FPGA**

The FPGA on the SMT417 implements the connectivity between *all* the external interfaces on the board and the DSPs. The FPGA can be reconfigured by the customer to provide any manner of connectivity within the system.

The following description of the FPGA functionality describes the default implementation that is provided by Sundance DSP upon initial delivery of the SMT417 Board Support package.

<sup>8</sup> See also SMT6012, the support package for CCS for Sundance carrier boards and modules.

| Document No.      | Revision | Date      | Page 20 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 age 20 01 72 |

<sup>&</sup>lt;sup>7</sup> <u>http://www.quicklogic.com/home.asp?menuID=110&PageID=319</u>

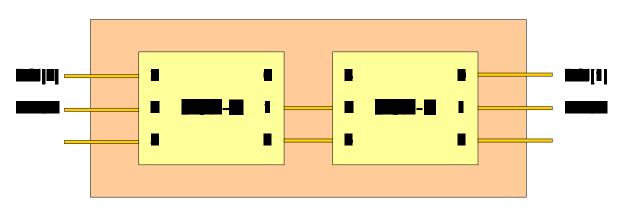

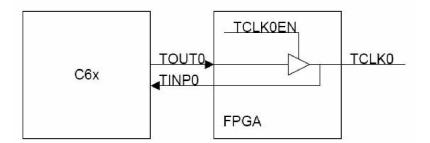

Figure 12 - Block diagram of SMT417 FPGA (v0.1)

The basic architecture implements an EMIF target interface to each of the DSPs. Each DSP accesses its resources independently and concurrently of the other. Resources such as comports, SDBs, the PCI interface and the user-defined blocks are memory mapped into the DSPs EMIF. The DSP's DMA engines and device drivers are responsible for pushing or pulling data to and from the resources respectively.

User-defined resources can be mapped into the EMIF as appropriate and necessary for the customer application. The most efficient way to do this is to "present" either a CP, SDB or RSL interface to the DSP's EMIF, and take advantage of existing software drivers on the DSP for this purpose.

The SMT417 Board Support Package provides the firmware sources (.vhd) for the basic architecture, as well as a means of customizing it under 3L Diamond/FPGA.

#### 4.4. DSP

Two TMS320C6416T signal processors are available on the SMT417. The TMS320C64x<sup>TM</sup> (C64x<sup>TM</sup>) device is based on the second-generation high-performance, advanced VelociTI<sup>TM</sup> very-long-instruction-word (VLIW) architecture (VelociTI.2<sup>TM</sup>) developed by Texas Instruments (TI). The C64x<sup>TM</sup> is a code-compatible member of the C6000<sup>TM</sup> DSP platform<sup>9</sup>.

<sup>&</sup>lt;sup>9</sup> <u>http://focus.ti.com/docs/prod/folders/print/tms320c6416t.html</u>

| Document No.      | Revision | Date      | Page 21 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 2             |

The DSP processors are excellent for performing image/signal processing, communications and implementing multiple-instruction, multiple-data (MIMD) algorithms.

The C64x<sup>TM</sup> DSP core processor has 64 general-purpose registers of 32-bit word length and eight independent functional units. This includes two multipliers for a 32-bit result and six arithmetic logic units. The C64x<sup>TM</sup> can produce four 16-bit multiply-accumulates (MACs) per cycle. The C6416T device has two high-performance embedded coprocessors [Viterbi Decoder Coprocessor (VCP) and Turbo Decoder Coprocessor (TCP)] that significantly speed up channel-decoding operations on-chip.

The C64x<sup>TM</sup> uses a two-level cache-based architecture. The Level 1 program cache (L1P) is a 128-Kbit direct mapped cache and the Level 1 data cache (L1D) is a 128-Kbit 2-way set-associative cache. The Level 2 memory/cache (L2) consists of an 8-Mbit (1M byte) memory space that is shared between program and data space. L2 memory can be configured as mapped memory or combinations of cache (up to 256K bytes) and mapped memory.

#### 4.4.1. EMIF Interface to FPGA

High-bandwidth connectivity between the DSP and the FPGA uses the same 64-bit, 133MHz EMIF signalling as on the DSP/SDRAM interface.

#### 4.4.2. FLASH

A single 512MB NAND FLASH memory device is attached to DSPA/EMIFB. This device enables the system bootstrap, default (or custom) FPGA bitstreams, and custom DSP application programs to be stored and executed on power-up or reset.

#### 4.4.3. HPI

The SMT417 implements the Host Port interface in the following way: One of DSPAs EMIFB regions is mapped to DSPBs HPI. This enables DSPA to access any register/memory region of DSPB. This is typically used for bootloading DSPB at system reset.

#### 4.4.4. McBSP

Each DSP has 3 multi-buffered serial ports. These are electrically connected to the FPGA and may be used by customers in any manner they wish. The default software interfaces provided by the SMT417 do not interface to these ports.

#### 4.4.5. PCI Interface

The built-in PCI interface on the DSP is *not implemented* on the SMT417.

#### 4.4.6. SDRAM

Each DSP has separate banks of SDRAM for local processing on EMIFA. 128MB of 64-bit SDRAM per DSP is populated on the board, based on two 512Mbit x32 parts per DSP (total of 256MB on board). The SDRAM is clocked at 133MHz.

#### **4.4.7. UTOPIA**

The built-in UTOPIA (Level 2 Slave ATM) interface on the DSP is not implemented on the SMT417.

| Document No.      | Revision | Date      | Page 22 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 60            |

#### 5. OPERATION

This section describes the operation of the various functions that can be used to control the SMT417. Note that all of these operations are handled by the device drivers, software and firmware that is distributed with the SMT417 Board Support Package.

From a HOST-Centric point of view, there are two non-volatile interfaces present at power-up. The QL5064 Bridge registers and the CPLD registers which are accessible after the QL5064 Bridge is setup. The CPLD provides access to basic board control as well as programming the FPGA.

#### 5.1. QL5064 BRIDGE SETUP

The SMT417 implements the "QL5064 Companion Design for SRAM FPGAs<sup>10</sup>". There are no deviations from the specifications of the external interfaces. The programming of the SMT417 FPGA, however, is handled by the SMT417 CPLD, rather than the capability offered by the QL5064<sup>11</sup>.

#### 5.1.1. ENABLE PCI ACCESS

The basic steps necessary to *begin* working with the SMT417 (from the PCI) are as follows:

- 1. Map the two primary memory regions, BAR0 and BAR1

- 2. Setup the BAR1-BAR4 bus region chip selects and timings for each of the bus region address spaces. The registers are in the BAR0 bus regions and indexed by constants given in q15064\_pci.h under "QLCD\_BAR0\_BUS\_REGION\_\*".

- a. The "\_LO\_" register enables the internal transfer acknowledge mode and associated bus cycle delays.

- b. The "\_HI\_" register controls the burst enable, CS line and the strobe delays.

- c. The regions are setup (by default) according to the following table:

| BAR         | Region | Wait<br>State | RD<br>Delay | WR<br>Delay | Burst | CS_SEL | Description       |

|-------------|--------|---------------|-------------|-------------|-------|--------|-------------------|

| 1           | 0-6    | 1             | 0           | 0           | NO    | 2      | CPLD Registers    |

| 1           | 7      | 2             | 0           | 1           | NO    | 1      | FPGA Link Ports   |

| 2-4,<br>DMA | 0-7    | 1             | 0           | 0           | YES   | 4-16   | FPGA Custom Logic |

Table 1 - Base Address Region Setup Parameters

d. *IMPORTANT*: consider enabling the 'Transfer Acknowledge' function on each of the regions when developing FPGA firmware. An unacknowledged transfer will result in an NMI/Parity Error on the HOST and shutdown the system. Any memory regions which are mapped as 'pre-fetchable' are subject to spontaneous access by the HOST.

<sup>&</sup>lt;sup>11</sup> This is different than the SMT407/SMT498 which *did* use this feature of the QL5064.

| Document No.      | Revision | Date      | Page 23 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 age 23 01 72 |

<sup>&</sup>lt;sup>10</sup> See: <u>http://www.quicklogic.com/images/QL5064\_CD\_UM.pdf</u>

3. Setup the BAR1-BAR4 bus request addresses. The registers are in the BAR0 bus regions and indexed by constants given in q15064\_pci.h under "QLCD\_BAR0\_REQAD\_BARn".

| Resource | Local Bus<br>Request<br>Address | Resource<br>Size | Prefetchable | Description              |

|----------|---------------------------------|------------------|--------------|--------------------------|

| BAR0     | N/A                             | 8KB              | NO           | QL5064 Registers         |

| BAR1     | 0x00000000                      | 1MB              | NO           | CPLD/FPGA Link Ports     |

| BAR2     | 0x00000000                      | 256MB            | NO           | FPGA Custom Logic        |

| BAR3     | 0x80000000                      | 256MB            | NO           | FPGA Custom Logic        |

| BAR4     | 0x00000000                      | 128MB            | YES          | DSPA SDRAM <sup>12</sup> |

| BAR5     | 0x00000000                      | 128MB            | YES          | DSPB SDRAM               |

Table 2 - Base Address Region Descriptions

- 4. Setup the DMA engine bus request addresses The registers are in the BAR0 bus regions and indexed by constants given in q15064\_pci.h under "QLCD\_BAR0\_REQAD\_DMA\_\*". The values are not important until the DMA engines are activated for I/O transfers. Disable the DMA controller.

- 5. Enable access to the local bus by setting bit 7 and bit 2 in the QLCD\_BAR0\_LB\_CTRL register.

- 6. Verify Read/Write access to QL5064 by performing the following actions:

- a. Write the channel 0 MWAR register at bar0[QL5064\_BAR0\_CH0\_MWAR].

- b. Read it back to ensure that it was written.

- c. Read the revision ID at bar0[QLCD\_BAR0\_REV\_ID].

- 7. The revision ID in #6.c, above determines if 'Bit Swizzling' needs to occur for CPLD accesses. If the revision id is 0xB0102, then this bit swizzling needs to occur prior-to and after any data access to BAR1 targeting the CPLD registers. A macro for this purpose is provided in smt417.h under the names: smt417CpldSwizzle() and smt417CpldDeswizzle().

- 8. Enable PCI operations by unlocking the CPLD as follows:

- a. Write SMT417\_CPLD\_MAGIC\_IDX into bar1[SMT417\_CPLD\_REGIDX\_ADR].

- b. Write SMT417\_CPLD\_MAGIC\_VALUE into bar1[SMT417\_CPLD\_REGS\_ADR].

#### 5.1.2. DISABLE PCI ACCESS

The basic steps necessary to stop working with the SMT417 (from the PCI) are as follows:

- 1. Disable PCI operations by locking the CPLD as follows:

- a. Write SMT417\_CPLD\_MAGIC\_IDX into bar1[SMT417\_CPLD\_REGIDX\_ADR].

<sup>&</sup>lt;sup>12</sup> BAR4,5 SDRAM mapping to PCI requires support in the FPGA design. This is planned, but not currently implemented. Contact Sundance DSP for details.

| Document No.      | Revision | Date      | Page 24 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 |               |

- b. Write 0 into bar1[SMT417\_CPLD\_REGS\_ADR].

- 2. Disable the DMA controller by writing 0 to bar0[QLCD\_BAR0\_DMA\_CTRL].

- 3. Unmap any memory regions which were mapped above.

#### 5.1.3. RESET

The basic steps necessary to reset the SMT417 (from the PCI) are as follows:

- 1. (optional) Save the state of the CPLD\_SMCTL and CPLD\_DSPJTAG registers.

- a. Write SMT417\_CPLD\_SMCTL\_IDX into bar1[SMT417\_CPLD\_REGIDX\_ADR].

- b. Read bar1[SMT417\_CPLD\_REGS\_ADR].

- c. Write SMT417\_CPLD\_DSPJTAG\_IDX into bar1[SMT417\_CPLD\_REGIDX\_ADR].

- d. Read bar1[SMT417\_CPLD\_REGS\_ADR].

- 2. Set the QLCD\_BAR0\_LB\_CTRL\_INIT\_LRST bit in QLCD\_BAR0\_LB\_CTRL register.

- 3. Hold for 25ms

- 4. Clear the QLCD\_BAR0\_LB\_CTRL\_INIT\_LRST bit in QLCD\_BAR0\_LB\_CTRL register.

- 5. Delay for 2.5 sec (to allow the system PLLs to resync, etc.)

- 6. Set the SMPROGB, SMINITB and FRESET bits in CPLD\_SMCTL.

- 7. Hold for 100ms

- 8. Clear the FRESET bit in CPLD\_SMCTL.

- a. You may consider the original state of the CPLD\_SMCTL bits saved in #1 above when writing the final value to the CPLD\_SMCTL register.

- b. Write SMT417\_CPLD\_SMCTL\_IDX into bar1[SMT417\_CPLD\_REGIDX\_ADR].

- c. Write bar1[SMT417\_CPLD\_REGS\_ADR].

- 9. Hold for 100ms

- 10. Clear the DSPRESET bit in the CPLD\_DSPJTAG register.

- a. You may consider the original state of the CPLD\_DSPJTAG bits saved in #1 above when writing the final value to the CPLD\_DSPJTAG register.

- b. Write SMT417\_CPLD\_DSPJTAG\_IDX into bar1[SMT417\_CPLD\_REGIDX\_ADR].

- c. Write bar1[SMT417\_CPLD\_REGS\_ADR].

| Document No.      | Revision | Date      | Page 25 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1450 25 01 72 |

#### 5.2. CPLD OPERATION

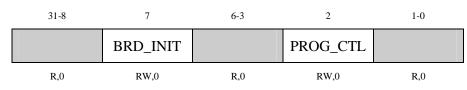

The CPLD is responsible for managing board reset state, linking the DSP JTAG, and programming the FPGA via SelectMAP. The CPLD provides 4 decode pages on the PCI, and two 8-bit registers on each page. The table below describes the location and meaning of the page registers.

| Resource | Local Bus<br>Request Address | Register<br>Size | Description              |

|----------|------------------------------|------------------|--------------------------|

| BAR1     | 0x000E0000                   | 8-bit            | CPLD Register Data Port  |

| BAR1     | 0x000E0008                   | 8-bit            | CPLD Register Index Port |

| BAR1     | 0x000E1000                   | 8-bit            | SelectMAP Data Port      |

| BAR1     | 0x000E2000                   | 8-bit            | DSP JTAG Data Port       |

| BAR1     | 0x000E3000                   | 8-bit            | Unassigned               |

|          | Table 2                      |                  | vistar Dagas             |

Table 3 - CPLD Register Pages

Within the first decode page (0xE0000), there are several CPLD registers which are accessible via the CPLD Register Data Port once the CPLD Register Index Port is written with the appropriate value.

See Section 7.2. below for details on the CPLD Registers bit assignments.

#### 5.2.1. CPLD MAGIC Register

The CPLD MAGIC (indexed at 0x40B) register is a read/write register enables PCI access to the board resources. This register must be written with the value SMT417\_CPLD\_MAGIC\_VALUE before normal PCI operations will be allowed to the higher order BARs and the FPGA. This value is defined in the header smt417.h included with the SMT417 Board Support Package.

| Document No.      | Revision | Date      | Page 26 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 420 20 01 72 |

#### 5.3. FPGA CONFIGURATION

The XC2VP50 FPGA present on the SMT417 may be configured by a variety of methods. The typical method is to have the DSPA bootloader (re-)load the FPGA configuration upon any reset of the board.

During application development, a user may wish to load/change the FPGA design often, and so the following methods are available.

#### 5.3.1. JTAG

The SMT417 provides an external JTAG port dedicated for the FPGA JTAG chain. This port is compatible with the Xilinx Parallel Cable IV and other JTAG emulators from Xilinx.

Figure 13 - Xilinx FPGA JTAG Port on JTAG Adapter

The JTAG adapter connects via a 20-pin ribbon cable between J2 on the SMT417 and J1 on the JTAG adapter. A standard 14-pin Xilinx JTAG is attached to J2 on the JTAG adapter, as pictured above. Once connected and powered, the CPLD, FPGA and QL5064 devices are present on the FPGA JTAG chain:

Figure 14 - Devices on the FPGA JTAG Chain

The programming files for the CPLD (XC2C256) and the QL5064 devices are provided in the SMT417 Board Support Package under firmware\smt417\. The pre-built programming files for the FPGA (XC2VP50) are also provided, but typically the user wishing to change the FPGA design will have their own .bit files that they wish to program.

Updating the FPGA design is simply a matter of selecting the device, and using the Xilinx iMPACT tool to program the bitstream. Please make note of the following caveats:

1. You should build your .bit with the DriveDone = YES flag set in the bitgen options.

| Document No.      | Revision | Date      | Page 27 of 72 |

|-------------------|----------|-----------|---------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 146027 0172   |

2. You should build your firmware to respect the nRESET control provided to the FPGA.

If you use 3L Diamond/FPGA to build your firmware, then please note the following (additional) caveat:

3. Diamond/FPGA will generate firmware that uses the DSPA EMIF clock as the default clock. Thus, when loading your FPGA design, you must ensure that the DSPs are taken out of reset. The DSP EMIF clock does not run when the DSP is held in reset.

#### 5.3.2. DSP via CPLD under Application Control

The FPGA can be programmed by DSPA through the CPLD. This can occur either at reset by the bootloader (typically), or by the users application at any other time. To do this, the SMCTL register is accessed by the DSP and the bitstream is loaded under the control of the DSP.

On the DSP, the SelectMAP control register is accessed at the address SMT417\_DSP\_CPLD\_SMCTL, which is provided in the smt417.h header file. See 7.2.2. below for the bit definitions. The manual procedure is as follows:

- 1. Set INIT and FRESET and clear RDWR and PROG.

- 2. Delay 100ms.

- 3. Set the PROG bit.

- 4. Delay 100ms.

- 5. Check the INIT and DONE bits. INIT must be '1' and DONE must be '0', otherwise the FPGA is not ready to receive a new bitstream.

- 6. Write all the words in the desired bitstream DWORD-wise to the SelectMAP Data Port mapped in the DSPAs address space at SMT417\_DSP\_CPLD\_SMD. The words can be sent in a burst, as the EMIFB timings have been designed to meet the specifications of the SelectMAP port on the FPGA.

- 7. Delay 100ms.

- 8. Check the INIT and DONE bits. Both INIT and DONE must be '1' if the FPGA has been successfully programmed.

An example and API for accomplishing this is provided in src\smt417\flash\hal\_smt417.c in the SMT417 Board Support Package.

#### **5.3.3.** DSP via CPLD under Bootload

The default bootloader provided with the SMT417 performs an FPGA bitstream load function, if an FPGA bitstream is loaded to the appropriate sectors of the on-board NAND FLASH memory device. This is perhaps the easiest way to configure the FPGA once it is developed. To use this feature, the .bit file must be programmed into the FLASH at the appropriate sector.

The smt417FlashTool application is provided for this purpose. The smt417FlashTool is designed to operate under CCS JTAG, so DSP JTAG connectivity must first be established. The source code for the smt417FlashTool is provided at src\smt417\flashtool\ in the SMT417 Board Support Package. Details on using the tool can be found in the SMT417 Installation Guide.

| Document No.      | Revision | Date      | Page 28 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 450 20 01 72 |

#### 5.3.4. PCI via CPLD

The SMT417 FPGA can be configured from the PCI. These functions are available to any application which uses the q15064\_hal.h API. Additionally several programs are distributed with the SMT417 Board Support Package to provide this facility from the command line.

The basic steps necessary to program the FPGA on the SMT417 (from the PCI) are as follows:

- 1. (optional) Hold the DSP in reset during this operation by setting the DSPRESET bit in the CPLD\_DSPJTAG register.

- 2. Assert PROG by clearing PROG and RDWR in the CPLD\_SMCTL register.

- 3. Delay for 100ms.

- 4. Set PROG, INIT and FRESET in the CPLD\_SMCTL register.

- 5. Delay for 100ms.

- 6. Check the INIT and DONE bits. INIT must be '1' and DONE must be '0', otherwise the FPGA cannot accept a new bitstream.

- 7. Write all the words of the bitstream BYTE-wise to the SelectMAP Data Port<sup>13</sup>.

- a. Write into bar1[SMT417\_CPLD\_SMDATA\_ADR].

- b. For every 1024 bytes, check the INIT bit in the CPLD\_SMCTL register.

- a. If the bit is '0', this indicates a configuration error of some sort, so stop.

- 8. Delay for 100ms

- 9. Check the INIT and DONE bits. Both must be '1', otherwise the FPGA did not configure.

- 10. Set the PROG, INIT and FRESET bits in the CPLD\_SMCTL register.

- 11. Hold for 100ms

- 12. (optional) If the DSP was held in reset in #1 above, release it.

- 13. Clear the FRESET bit in the CPLD\_SMCTL register.

- 14. Delay for 100ms.

- 15. (optional) Configure the I/O link ports in the FPGA which provide connectivity to the FPGA from the PCI. To do this, index the link port's CSR register and set the TRIGSIZE() value for each link port. Toggle the RESET bit on the port as well. These operations are done in the ql5064\_hal.c and the ql5064\_hal.h API.

$<sup>^{13}</sup>$  You may want to parse the .bit header and only send the RAW data to the device, but the FPGA accepts the header portion of the .bit file.

| Document No.      | Revision | Date      | Page 29 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 450 29 01 72 |

#### 5.4. FPGA I/O INTERFACES

This section describes the operation of the various I/O interfaces which are present on the SMT417 board. Since all of the important interfaces are connected to the FPGA, any of these descriptions can be modified by users of the SMT417 for their custom application needs. This section describes the *default* firmware design which is provided in the SMT417 Board Support Package.

#### 5.4.1. Comports

Comports are implemented in order to allow communication between the DSPs. The presentation of the comport to the DSP is described in the Sundance literature<sup>14,15</sup>.

Figure 15 - Comport Links to DSPs

The diagram above describes the mapping of comport links between external resources and the DSPs. These links are implemented in the FPGA; each DSP accesses its comports via memory-mapped I/O in its respective EMIF(A) address space.

The comport interface includes a status register indicating the current port direction and number of FIFO entries (for each direction). The interface has a minimum transfer unit of 1 (32-bit) DWORD. Interrupts generated by comports are routed through standard Sundance interfaces described above.

#### 5.4.2. PCI

A comport-like interface is established between each DSP and the PCI bridge. These are mapped as standard comports with respect to the DSP, and as the link ports described below with respect to the PCI. The main differences between this interface and a standard comport are as follows:

- 1) Separate ports for inbound/outbound data and control. I.e. link ports are uni-directional

- 2) 64-bit wide I/O capability.

- 3) 1024 (64-bit) QWORD FIFO depth in the FPGA.

<sup>&</sup>lt;sup>15</sup> <u>http://www.sundance.com/docs/Firmware.pdf</u>

| Document No.      | Revision | Date      | Page 30 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 age 50 01 72 |

<sup>&</sup>lt;sup>14</sup> <u>http://www.sundance.com/docs/SMT6400.chm</u>

The SMT417 Board Support Package provides source code, drivers and applications which describe the use of the link ports for I/O between the DSPs. Please refer to Section 7.3. below for register details.

#### 5.4.3. SHB

The Sundance High Speed Bus<sup>16</sup> is implemented to allow high-bandwidth digital data transport to occur between modules. The SHBs can be configured for data widths of 16, or 32-bits, typically<sup>17</sup>. The presentation of the SDB interface is also described in the Sundance literature.

Figure 16 - SHB Links to DSPs

The firmware loaded onto the FPGA determines the organization of the SDB and which ports are connected to which DSPs. On multi-DSP modules, it is common to provide an SDB link through the FPGA. See the release notes for your version of the SMT417 Board Support Package for specific details.

<sup>&</sup>lt;sup>17</sup> Multiple 8-bit and other interfaces can also be accommodated. Contact Sundance DSP for details on special firmware support.

| Document No.      | Revision | Date      | Page 31 of 72  |

|-------------------|----------|-----------|----------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | 1 age 51 01 72 |

<sup>&</sup>lt;sup>16</sup> The Sundance Digital Bus (SDB) is used interchangeably. The physical layer protocol is identical with only the number of bits available on the connector being different. The SMT417 implements a full-specification SHB connector (60 signals).

#### 5.4.4. MGTs

The XC2VP50 provides 16 Multi-Gigabit Transceiver pairs. These are routed to several connectors on the SMT417. All RX links are AC-coupled on the FPGA.

- 1. A Sundance RSL connector implements 7 bidirectional links. Note, that the RSL specification defines only 6 bidirectional pairs, but the connector allows for 14 signal pairs, so the 7<sup>th</sup> link is connected.

- 2. The XMC connector implements 8 bidirectional links according to ANSI/VITA 42.2 (Serial RapidIO for XMC).

- 3. A set of 4 coaxial connectors in a high-density mounting (5mm x 32.20mm) from Samtec. The <u>GRF1-J</u> PCB connector mates with a <u>GRF1-C</u> cable end to provide a means to expose a single 1x bidirectional link.

Please see Section 9.4. 9.6. 9.7. for details on the pin locations at the connectors. The table below describes the different resources and their location on the FPGA.

| Location  | IOB   | Resource | Lane | Termination<br>Power | CLOCK        | Connector |

|-----------|-------|----------|------|----------------------|--------------|-----------|

| A30-A33   | X0_Y1 | RSL      | 3    | VRIOA                | TOP.BREFCLK  | JA6       |

| A26-A29   | X1_Y1 | XMC      | 0    | VRIOA                | TOP.BREFCLK  | J5        |

| A22-A25   | X2_Y1 | XMC      | 4    | VRIOA                | TOP.BREFCLK  | J5        |

| A18-A21   | X3_Y1 | XMC      | 1    | VRIOA                | TOP.BREFCLK  | J5        |

| A14-A17   | X4_Y1 | XMC      | 2    | VRIOA                | TOP.BREFCLK  | J5        |

| A10-A13   | X5_Y1 | XMC      | 5    | VRIOA                | TOP.BREFCLK  | J5        |

| A6-A9     | X6_Y1 | XMC      | 3    | VRIOA                | TOP.BREFCLK  | J5        |

| A2-A5     | X7_Y1 | RSL      | 4    | VRIOA                | TOP.BREFCLK  | JA6       |

| AP2-AP5   | X7_Y0 | RSL      | 5    | VRIOB                | BOT.BREFCLK2 | JA6       |

| AP6-AP9   | X6_Y0 | GRF      | 0    | VRIOB                | BOT.BREFCLK2 | JA5       |

| AP10-AP13 | X5_Y0 | XMC      | 6    | VRIOB                | BOT.BREFCLK2 | J5        |

| AP14-AP17 | X4_Y0 | RSL      | 0    | VRIOB                | BOT.BREFCLK2 | JA6       |

| AP18-AP21 | X3_Y0 | RSL      | 1    | VRIOB                | BOT.BREFCLK2 | JA6       |

| AP22-AP25 | X2_Y0 | XMC      | 7    | VRIOB                | BOT.BREFCLK2 | J5        |

| AP26-AP29 | X1_Y0 | RSL      | 2    | VRIOB                | BOT.BREFCLK2 | JA6       |

| AP30-AP33 | X0_Y0 | RSL      | 6    | VRIOB                | BOT.BREFCLK2 | JA6       |

Table 4 - MGT Cross-Reference for SMT417 PCB V2

| Document No.      | Revision | Date      | $\mathbf{D}_{a,aa} = 22 \text{ of } 72$ |

|-------------------|----------|-----------|-----------------------------------------|

| SMT417 User Guide | 0.3      | 27-Feb-07 | Page 32 of 72                           |

#### 5.4.4.1. FPGA Options

The FPGA device is an XC2VP50 of package type FF1152. In order to support the 637 total I/Os required by this design, the minimum device size will be a VP30. A VP50 is the minimum size that supports all 16 RSL links possible on this board. The table below shows the number and allocation of MGTs for different FPGA devices.

| Device  | XMC<br>Lanes | RSL<br>Lanes | GRF-1 |

|---------|--------------|--------------|-------|

| XC2VP30 | 4            | 3            | 1     |

| XC2VP40 | 4            | 7            | 1     |

| XC2VP50 | 8            | 7            | 1     |

Table 5 - MGT Allocation vs. FPGA Size

#### 5.4.4.2. Presentation to the DSP

Use of the MGTs via the DSP will be provided under 3L Diamond/FPGA under the RSL protocol. Contact Sundance DSP for details on accessing the MGTs apart from Diamond/FPGA or the RSL protocol.

#### 5.4.4.3. Clock Source

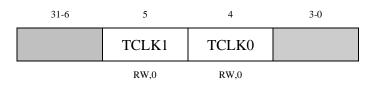

When using the MGTs, it is important to consider the geographical location of the MGT pairs with respect to the available clock source. The possible clocks for the MGTs are as follows: